July 2013

# FAN7340 LED Backlight Driving Boost Switch

#### **Features**

- Single-Channel Boost LED Switch

- Internal Power MOSFET for PWM Dimming: R<sub>DS(on)</sub> = 3.4 Ω at V<sub>GS</sub>=10 V, BV<sub>DSS</sub>=400 V

- Current Mode PWM Control

- Internal Programmable Slope Compensation

- Wide Supply Voltage Range: 10 V to 35 V

- LED Current Regulation: ±1%

- Programmable Switching Frequency

- Analog and PWM Dimming

- Wide Dimming Ratio: On Time=10 µs to DC

- Cycle-by-Cycle Current Limiting

- Thermal Shutdown: 150°C

- Open-LED Protection (OLP)

- Over-Voltage Protection (OVP)

- Over-Current Protection (OCP)

- Error Flag Generation (for External Load Switch)

- Internal Soft-Start

- 16-Lead SOIC Package

### **Applications**

- LED Backlight for LCD TV

- LED Backlight for LCD Monitor

- LED Lighting

### **Description**

The FAN7340 is a single-channel boost controller that integrates an N-channel power MOSFET for PWM dimming using Fairchild's proprietary planar Double-diffused MOS (DMOS) technology.

The IC operates as a constant-current source for driving high-current LEDs.

It uses Current Mode control with programmable slope compensation to prevent subharmonic oscillation. The IC provides protections including: open-LED protection, over-voltage protection, and direct-short protection for high system reliability.

The IC internally generates a FAULT signal with delay if an abnormal LED string condition occurs. PWM dimming and analog dimming functions can be implemented independently. Internal soft-start prevents inrush current flowing into output capacitor at startup.

## **Ordering Information**

| Part Number | Operating<br>Temperature<br>Range | Package                                          | Packaging<br>Method |

|-------------|-----------------------------------|--------------------------------------------------|---------------------|

| FAN7340MX   | -40°C to +125°C                   | 16-Lead, Small-Outline Integrated Circuit (SOIC) | Tape & Reel         |

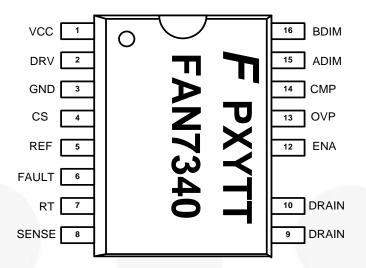

## **Pin Assignments**

Figure 2. Package Diagram

### **Pin Definitions**

| Pin#  | Name  | Description                                                                                                                                                                                                                                                                                                   |  |  |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | VCC   | This pin is the supply voltage of the IC.                                                                                                                                                                                                                                                                     |  |  |

| 2     | DRV   | This pin is the gate drive signal of the boostswitch.                                                                                                                                                                                                                                                         |  |  |

| 3     | GND   | This pin is the ground of the IC.                                                                                                                                                                                                                                                                             |  |  |

| 4     | CS    | This pin is for sensing the current flowing through an external MOSFET. It includes a built-in 300 ns blanking time. The peak of the current flowing through the MOSFET is limited to this pin voltage. Slope compensation of the boost controller can be programmed through the series resistor of this pin. |  |  |

| 5     | REF   | This pin is the 5 V reference voltage pin. Maximum current capability is 3 mA.                                                                                                                                                                                                                                |  |  |

| 6     | FAULT | This pin is for indicating the fault signal. This pin is connected to the open drain. When OLP protection is occurred, the FAULT pin is pulled HIGH.                                                                                                                                                          |  |  |

| 7     | RT    | Oscillator frequency set of the boost switch (50 kHz ~ 300 kHz).                                                                                                                                                                                                                                              |  |  |

| 8     | SENSE | This pin is for sensing the current flowing through the LEDs. A sensing resistor is connected from this pin to ground. This pin is connected to the negative input of the internal error amplifier.                                                                                                           |  |  |

| 9, 10 | DRAIN | Drain pin of PWM dimming power MOSFET.                                                                                                                                                                                                                                                                        |  |  |

| 12    | ENA   | Enable input pin. If voltage of this pin is higher than 1.22 V, IC is starting to operate. If the voltage of this pin is lower than 1.15 V, the IC stops operating.                                                                                                                                           |  |  |

| 13    | OVP   | Over-voltage protection input pin. Output voltage of the boost circuit is connected to this pin through a resistor divider circuit. If this pin voltage is higher than 3 V, OVP is triggered.                                                                                                                 |  |  |

| 14    | CMP   | This pin is the error amplifier output. Typically, a compensation capacitor and resistor are connected to this pin from the ground.                                                                                                                                                                           |  |  |

| 15    | ADIM  | This pin is for setting the current flowing through the LEDs. This pin is connected to the positive inputs of the internal error amplifier. Linear voltage range of ADIM is 0.3 V~3.0 V.                                                                                                                      |  |  |

| 16    | BDIM  | This pin is for the burst dimming signal. If this pin voltage is HIGH, the internal dimming MOSFET is turned on. If this pin voltage is LOW, the dimming MOSFET is turned off.                                                                                                                                |  |  |

#### Note:

1. Pin 11 is a "No Connect" pin (not shown in Figure 2).

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. T<sub>A</sub>=25°C unless otherwise specified.

| Symbol           | Parameter                                                | Min. | Max. | Unit |

|------------------|----------------------------------------------------------|------|------|------|

| Vcc              | Supply Voltage                                           | 10   | 35   | V    |

| T <sub>A</sub>   | Operating Temperature Range                              | -40  | +125 | °C   |

| TJ               | Junction Temperature                                     |      | +150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                | -65  | +150 | °C   |

| ӨЈА              | Thermal Resistance Junction-to-Ambient <sup>(2, 3)</sup> |      | 120  | °C/W |

| P <sub>D</sub>   | Power Dissipation                                        |      | 0.9  | W    |

#### Notes:

- Thermal resistance test board; size 76.2 mm x 114.3 mm x 1.6 mm (1SOP); JEDEC standard: JESD51-2, JESD51-3.

- 3. Assume no ambient airflow.

## Pin Breakdown Voltage

| Pin# | Name  | Value | Unit |

|------|-------|-------|------|

| 1    | VCC   | 35    | V    |

| 2    | DRV   | 20    | V    |

| 3    | GND   |       | V    |

| 4    | CS    | 6     | V    |

| 5    | REF   | 6     | V    |

| 6    | FAULT | 35    | V    |

| 7    | RT    | 6     | V    |

| 8    | SENSE | 6 V   |      |

| Pin # | Name  | Value | Unit |

|-------|-------|-------|------|

| 9     | DRAIN | 400   | V    |

| 10    | DRAIN | 400   | V    |

| 11    | N/A   |       | V    |

| 12    | ENA   | 6     | V    |

| 13    | OVP   | 6     | V    |

| 14    | CMP   | 6     | V    |

| 15    | ADIM  | 6     | ٧    |

| 16    | BDIM  | 6     | V    |

#### **Electrical Characteristics**

For typical values,  $T_A = 25^{\circ}\text{C}$  and  $V_{CC} = 15~\text{V}$  unless otherwise specified. Specifications to -40°C ~ 125°C are guaranteed by design based on final characterization results .

| Symbol                     | Parameter                                       | Condition                                                            | Min. | Тур.  | Max. | Unit  |

|----------------------------|-------------------------------------------------|----------------------------------------------------------------------|------|-------|------|-------|

| Supply Volta               | age Section                                     |                                                                      | •    | •     |      |       |

| Vcc                        | Input DC Supply Voltage Range (4)               |                                                                      | 10   |       | 35   | V     |

| I <sub>SD</sub>            | Shutdown Mode Supply Current                    | BDIM Connected to GND                                                |      | 2     | 4    | mΑ    |

| Under-Volta                | ge Lockout Section                              |                                                                      | •    | •     |      |       |

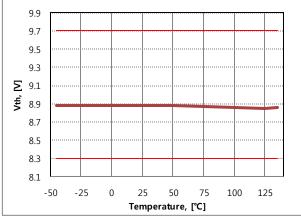

| $V_{th}$                   | Start Threshold Voltage                         |                                                                      | 8.3  | 9.0   | 9.7  | V     |

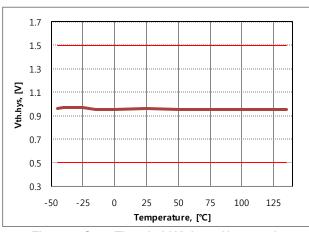

| V <sub>th,hys</sub>        | Start Threshold Voltage Hysteresis              |                                                                      | 0.5  | 1.0   | 1.5  | V     |

| I <sub>st</sub>            | Standby Current                                 | $V_{CC}=V_{th}$ -0.2                                                 |      | 200   | 300  | μΑ    |

| ON/OFF Sec                 | ction                                           |                                                                      |      |       |      |       |

| V <sub>on</sub>            | On-State Input Voltage                          |                                                                      | 2    |       | 5    | V     |

| V <sub>off</sub>           | Off-State Input Voltage                         |                                                                      |      |       | 0.8  | V     |

| Error Ampli                | fier Section                                    |                                                                      |      |       |      |       |

| Gm                         | Error Amplifier Transconductance <sup>(4)</sup> | V <sub>ADIM</sub> =1 V                                               | 100  | 300   | 500  | µm ho |

| A <sub>V_ro</sub>          | Error Amplifier Output impedance (4)            |                                                                      |      | 20    |      | ΜΩ    |

| A <sub>V</sub>             | Error Amplifier Open-Loop Gain <sup>(4)</sup>   |                                                                      |      | 60    |      | dB    |

| V <sub>offset</sub>        | Input Offset Voltage                            | V <sub>ADIM</sub> =1 V                                               | -10  |       | 10   | mV    |

| I <sub>sin</sub>           | CMP Sink Current                                | V <sub>ADIM</sub> =1 V, V <sub>SEN SE</sub> =2 V                     | 100  | 200   | 300  | μA    |

| I <sub>sur</sub>           | CMP Source Current                              | V <sub>ADIM</sub> =1 V, V <sub>SENSE</sub> =0 V                      | 100  | 200   | 300  | μA    |

| V <sub>IDR</sub>           | Input Differential Voltage Range                | ,                                                                    | 0    | Ų.    | 3    | V     |

| Vo                         | Output Voltage Range                            |                                                                      | 0.7  |       | 4.0  | V     |

| Oscillator S               |                                                 |                                                                      |      |       |      |       |

|                            |                                                 | Min.                                                                 |      | 50    |      | kHz   |

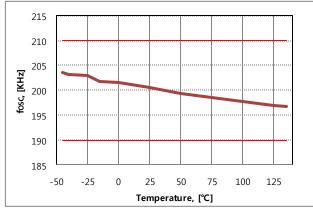

| f <sub>osc</sub>           | Boost Oscillator Frequency                      | R <sub>T</sub> =100 kΩ                                               | 190  | 200   | 210  | kHz   |

| 555                        |                                                 | Max.                                                                 |      | 300   |      | kHz   |

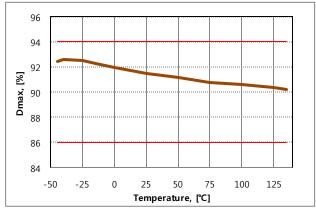

| D <sub>max</sub>           | Maximum Duty Cycle <sup>(4)</sup>               |                                                                      | 86   | 90    | 94   | %     |

| Reference S                |                                                 |                                                                      |      |       |      |       |

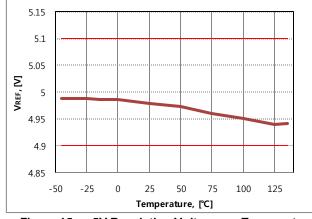

| V <sub>REF</sub>           | 5V Regulation Voltage                           |                                                                      | 4.9  | 5.0   | 5.1  | V     |

| V <sub>REF, Line</sub>     | 5V Line Regulation                              |                                                                      | / /  |       | 25   | mV    |

| V <sub>REF,Load</sub>      | 5V Load Regulation                              | 0 <i5<3 ma<="" td=""><td></td><td></td><td>25</td><td>mV</td></i5<3> |      |       | 25   | mV    |

| PWM Dimm                   |                                                 | 0 110 10 11111                                                       |      |       |      |       |

| V <sub>PDIM,L</sub>        | PWM Dimming Input Low Voltage                   |                                                                      |      | - 7   | 0.8  | V     |

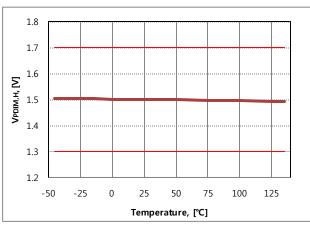

| V <sub>PDIM,H</sub>        | PWM Dimming Input High Voltage                  |                                                                      | 2    |       | 5    | V     |

| R <sub>PDIM</sub>          | PWM Dimming Pull-Down Resistance                |                                                                      | 100  | 160   | 220  | kΩ    |

|                            | (for Dimming)                                   |                                                                      | 100  | 1 .00 | 220  | 1142  |

|                            | Drain-Source Breakdown Voltage (4)              | V 0.V 1 250 ·· A                                                     | 400  |       |      | V     |

| BV <sub>DSS</sub>          |                                                 | V <sub>CC</sub> =0 V, I <sub>D</sub> =250 μA                         | 400  |       |      |       |

| I <sub>DSS</sub>           | Zero-Gate-Voltage Drain Current <sup>(4)</sup>  | V <sub>DS</sub> =250 V, T <sub>A</sub> =25°C                         | 1    | 1     | 30   | μA    |

| $R_{\text{DS}(\text{ON})}$ | Drain-Source On-State Resistance                | $V_{GS}$ =10 V, $I_{D}$ =1 A                                         |      | 3.4   |      | Ω     |

| C <sub>ISS</sub>           | Input Capacitance <sup>(4)</sup>                | V <sub>DS</sub> =25 V, V <sub>GS</sub> =0 V, f=1 MHz                 |      | 173   | 225  | pF    |

| Coss                       | Output Capacitance <sup>(4)</sup>               | V <sub>DS</sub> =25 V,V <sub>GS</sub> =0V, f=1 MHz                   |      | 30    | 40   | pF    |

Continued on the following page...

## **Electrical Characteristics** (Continued)

For typical values,  $T_A = 25^{\circ}C$  and  $V_{CC} = 15 \text{ V}$ , unless otherwise specified. Specifications to -25°C ~ 85°C are guaranteed by design based on final characterization results .

| Symbol                    | Parameter                                                      | Condition                 | Min.                   | Тур.                  | Max.                   | Unit |

|---------------------------|----------------------------------------------------------------|---------------------------|------------------------|-----------------------|------------------------|------|

| Output Se                 | ection (Boost / Dimming)                                       | 1                         |                        |                       |                        | .1   |

| $V_{DRV}$                 | Gate Output Voltage                                            | V <sub>CC</sub> =15 V     | 10.8                   | 11.8                  | 12.8                   | V    |

| $V_{uv}$                  | Gate Output Voltage Before Startup                             |                           | -0.5                   |                       | 0.5                    | V    |

| I <sub>dsur</sub>         | Gate Output Drive Source Current <sup>(4)</sup>                |                           | 80                     | 180                   | 280                    | mΑ   |

| I <sub>dsin</sub>         | Gate Output Drive Sink Current <sup>(4)</sup>                  |                           | 80                     | 180                   | 280                    | mΑ   |

| <b>t</b> rh               | Gate Output Rising Time (Boost) <sup>(4)</sup>                 | C <sub>L</sub> =2.0 nF    |                        | 200                   |                        | ns   |

| t <sub>fl</sub>           | Gate Output Falling Time (Boost) (4)                           | C <sub>L</sub> =2.0 nF    |                        | 120                   |                        | ns   |

| Current S                 | ense Section                                                   |                           |                        |                       |                        | .1   |

| <b>t</b> <sub>blank</sub> | Leading-Edge Blanking <sup>(4)</sup>                           |                           | 150                    | 300                   | 450                    | ns   |

| t <sub>delay,cl</sub>     | Delay to Output of Current-Limit<br>Comparator <sup>(4)</sup>  |                           |                        |                       | 180                    | ns   |

| V <sub>offset,clc</sub>   | Offset Voltage of Current-Limit<br>Comparator <sup>(4)</sup>   |                           | -20                    |                       | 20                     | mV   |

| Slope Co                  | mpensation Section                                             |                           |                        |                       |                        | .1   |

| I <sub>slope</sub>        | Ramp Generator Current                                         |                           | 36                     | 45                    | 54                     | μΑ   |

| R <sub>slope</sub>        | Slope Compensation Resistor (4)                                |                           |                        | 5                     | 1                      | kΩ   |

| Soft-Start                | Section                                                        |                           | '                      | V                     |                        |      |

| t <sub>ss</sub>           | Soft-Start Period <sup>(4)</sup>                               | f <sub>osc</sub> =200 kHz |                        | 3                     |                        | ms   |

| Protectio                 | n Section                                                      |                           | '                      |                       |                        |      |

| t <sub>d,ovp.tr</sub>     | Delay for Triggering Over-Voltage<br>Protection <sup>(4)</sup> |                           | 15                     | 20                    | 25                     | μs   |

| t <sub>d,ovpr</sub>       | Delay for Releasing Over-Voltage<br>Protection <sup>(4)</sup>  | y                         | 10                     | 14                    | 18                     | μs   |

| t <sub>d.ocp</sub>        | Delay for Over-Current Protection <sup>(4)</sup>               |                           |                        | 1                     |                        | μs   |

| t <sub>AR</sub>           | Auto-Restart Time for Over-Current Protection (4)              | f <sub>osc</sub> =200 kHz |                        | 640                   | Í                      | μs   |

| t <sub>d,ol pi</sub>      | Delay for Triggering Open-LED Protection (4)                   |                           | 3                      | 5                     | 7                      | μs   |

| t <sub>d,olp</sub>        | Delay for Open-LED Protection                                  | f <sub>osc</sub> =200 kHz |                        | 40.96                 |                        | ms   |

| $V_{th,ovp}$              | Over-Voltage Protection Threshold Voltage                      |                           | 2.85                   | 3.00                  | 3.15                   | V    |

| V <sub>hys,ovp</sub>      | Over-Voltage Protection Voltage Hysteresis                     |                           | <u> </u>               | 0.1                   |                        | V    |

| V <sub>th.csocp</sub>     | Boost Switch Current Limit Threshold<br>Voltage                |                           | 0.45                   | 0.50                  | 0.55                   | V    |

| V <sub>th,ocp</sub>       | LED Over-Current Protection Threshold Voltage                  |                           | 1.4<br>(Min.<br>Clamp) | 4.0xV <sub>ADIM</sub> | 4.0<br>(Max.<br>Clamp) | V    |

| $V_{th,olp}$              | Open-LED Protection Threshold Voltage (4)                      |                           | 0.15                   | 0.20                  | 0.25                   | V    |

| $T_{SD}$                  | Thermal Shutdown Temperature <sup>(4)</sup>                    |                           | 140                    | 150                   | 160                    | °C   |

| T <sub>HYS</sub>          | Thermal Shutdown Hysteresis (4)                                |                           |                        | 20                    |                        | °C   |

#### Notes:

4. These parameters, although guaranteed, are not tested in production.

## **Typical Performance Characteristics**

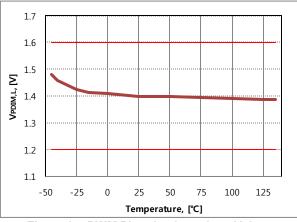

Figure 3. Start Threshold Voltage vs. Temperature

Figure 4. Start Threshold Voltage Hysteresis vs. Temperature

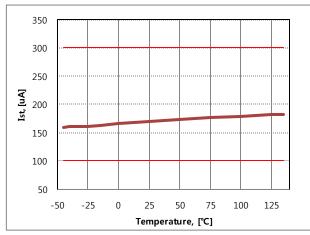

Figure 5. Standby Current vs. Temperature

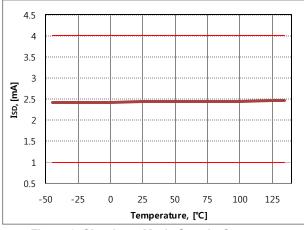

Figure 6. Shutdown Mode Supply Current vs. **Temperature**

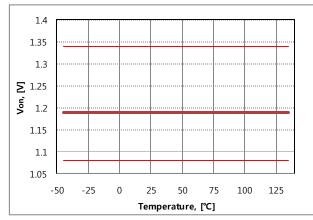

Figure 7. On-State Input Voltage vs. Temperature

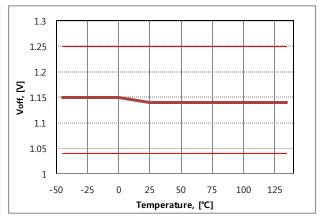

Figure 8. Off-State Input Voltage vs. Temperature

## **Typical Performance Characteristics** (Continued)

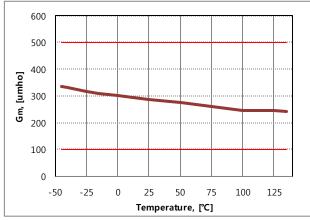

Figure 9. Error Amplifier Transconductance vs. Temperature

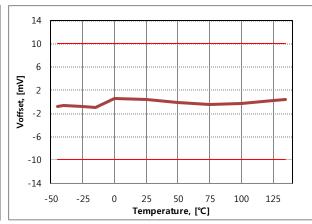

Figure 10. Input Offset Voltage vs. Temperature

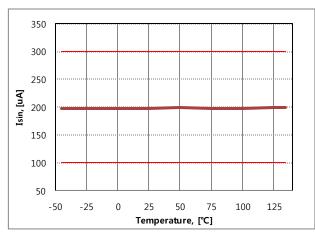

Figure 11. CMP Sink Current vs. Temperature

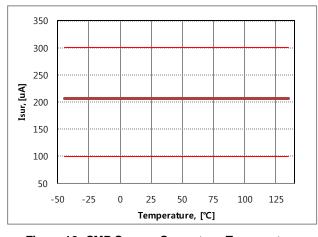

Figure 12. CMP Source Current vs. Temperature

Figure 13. Boost Oscillator Frequency vs. Temperature

Figure 14. Maximum Duty Cycle vs. Temperature

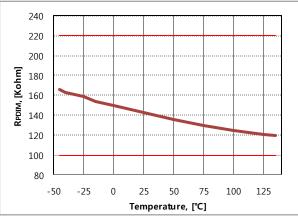

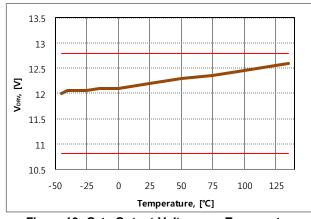

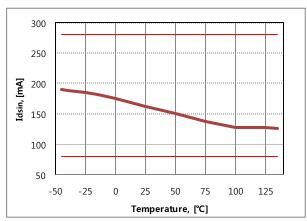

### **Typical Performance Characteristics** (Continued)

Figure 15. 5V Regulation Voltage vs. Temperature

Figure 16. PWM Dimming Input High Voltage vs. Temperature

Figure 17. PWM Dimming Input Low Voltage vs. Temperature

Figure 18. PWM Dimming Pull-Down Resistance vs. Temperature

Figure 19. Gate Output Voltage vs. Temperature

Figure 20. Gate Output Drive Sink Current vs. Temperature

## **Typical Performance Characteristics** (Continued)

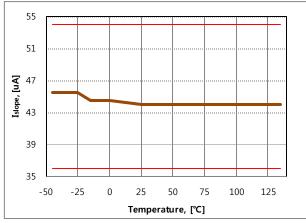

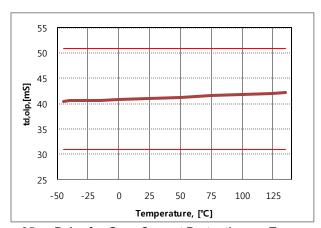

Figure 21. Ramp Generator Current vs. Temperature

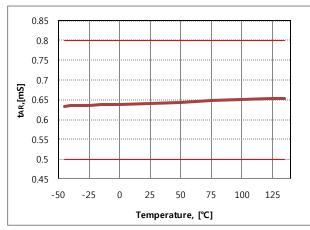

Figure 22. Auto-Restart Time for OCP vs. Temperature

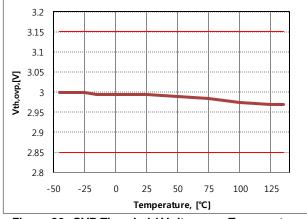

Figure 23. OVP Threshold Voltage vs. Temperature

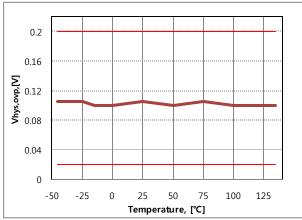

Figure 24. OVP Hysteresis Voltage vs. Temperature

Figure 25. Delay for Over-Current Protection vs. Temperature

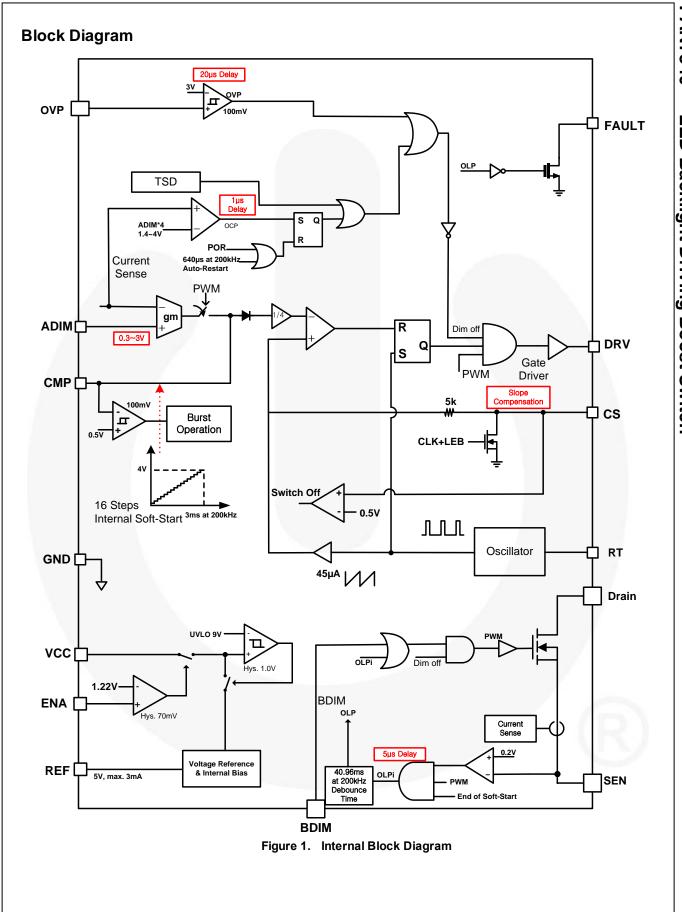

### **Functional Description**

The FAN7340 operates as a constant-current source for driving high-current LEDs. It uses Current-Mode control with programmable slope compensation to prevent sub-harmonic oscillation.

The IC provides protections such as open-LED protection, over-voltage protection, and over-current protection for improved system reliability. The IC internally generates a FAULT OUT signal with a delay in case an abnormal LED string condition occurs. PWM dimming and analog dimming functions can be implemented independently. Internal soft-start prevents inrush current flowing into output capacitor at startup. Circuit operation is explained in the following sections.

#### V<sub>cc</sub> Under-Voltage Lockout (UVLO)

An internal regulator provides the regulated 5 V used to power the IC. The Under-Voltage Lockout (UVLO) turns off the IC in the event of the voltage dropping below the specific threshold level. The UVLO circuit inhibits powering the IC until a voltage reference is established, up to predetermined threshold level.

#### **Enable**

Applying voltage higher than 1.22 V (typical) to the ENA pin enables the IC. Applying voltage lower than 1.15 V (typical) to the ENA pin disables the IC. If ENA pin voltage is higher than 1.22 V (typical) and  $V_{\rm CC}$  is higher than 9.0 V (typical.), the IC starts to supply 5 V reference voltage from  $V_{\rm CC}$ .

### Oscillator (Boost Switching Frequency)

Boost switching frequency is programmed by the value of the resistor connected from the RT pin to ground. RT pin voltage is set to 2 V. The current through the RT pin resistor determines boost switching frequency according to formula:

$$f_{OSC} = \frac{1}{(46.5 \times RT[k\Omega] + 350) \times 10^{-6}} [kHz]$$

(1)

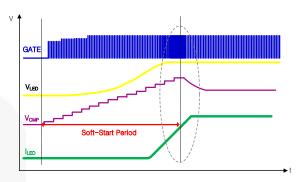

#### **Soft-Start Function at Startup**

During initial startup, the switching device can be damaged due to the over-current coming from the input line by the negative control. This can result in the initial overshoot of the LED current. Therefore, during initial startup, the soft-start control gradually increases the duty cycle so that the output voltage can rise smoothly to control inrush current and overshoot.

FAN7340 adapts the soft-start function in the boost converter stage. During soft-start period, boost switch turn-on duty is limited by clamped CMP voltage. The soft-start period is dependent on boost switching frequency, which is decided by the RT resistor (Equation (1)). Soft-start period is set to be cumulative time when the BDIM (PWM dimming) signal is HIGH:

$$T_{SS} = 600 / f_{OSC} [sec]$$

(2)

Figure 26. Soft-Start Waveforms

### **LED Current Setting**

During the boost converter operating periods, the output LED current can be set by equation:

$$I_{LED} = \frac{ADIM(V)}{R_{CENSE} + 60m\Omega}$$

(3)

where ADIM(V) is ADIM pin applied voltage and,  $R_{\text{SENSE}}$  is the sensing resistor value. An additional  $60\,\text{m}\Omega$  comes from an internal wire bonding resistor. To calculate LED current precisely, consider the wire bonding resistor.

### **Analog Dimming and PWM Dimming**

Analog dimming is achieved by varying the voltage level at the ADIM pin. This can be implemented either with a potentiometer from the VREF pin or from an external voltage source and a resistor divider circuit. The ADIM voltage level is adjusted to be the same as the feedback level (V<sub>SENSE</sub>). A V<sub>ADIM</sub> range from 0.3 V to 3 V is recommended.

PWM dimming (BDIM) helps achieve a fast PWM dimming response in spite of the shortcomings of the boost converter. The PWM dimming signal controls three nodes in the IC; gate signal to the switching FET, gate signal to the dimming FET, and output connection of the trans-conductance amplifier. When the PWM dimming signal is HIGH, the gates of the switching FET and dimming FET are enabled. At the same time, the output of the transconductance ap-amp is connected to the compensation network. This allows the boost converter to operate normally.

#### **Dynamic Contrast Ratio**

The Dynamic Contrast Ratio (DCR) means the maximum contrast ratio achievable by adjusting the amount of light (dimming) of the screen instantaneously using the backlight during the extremely short period of time. FAN7340 can normally drive the LED backlight under 0.1% dimming duty cycle at 200 Hz dimming frequency. Even operating at 5 µs-dimming FET turn-on time and extremely low dimming duty, FAN7340 can operate LEDs with normal peak current level.

### **Internal Dimming MOSFET**

A dimming MOSFET (400 V N-channel MOSFET; such as FDD3N40) is incorporated in the FAN7340. The power transistor is produced using Fairchild's proprietary, planar stripe, DMOS technology. This advanced technology is tailored to minimize on-state resistance ( $R_{DS(\text{on})}{=}3.4~\Omega)$ , to provide superior switching performance. This device is suited for high-efficiency SMPS and shows desirable thermal characteristic during operation. To prevent initial LED current overshoot at low  $V_{\text{ADIM}}$  levels, gate resistance of the internal dimming FET is designed as 5 k $\Omega$  experimentally.

#### **Feedback Loop Compensation**

Stable closed-loop control can be accomplished by connecting a compensation network between COMP and GND. The compensation needed to stabilize the converter can be either a Type-I circuit (a simple integrator) or a Type-II circuit (and integrator with and additional pole-zero pair). The type of the compensation circuit required is dependent on the phase of the power stage at the crossover frequency.

FAN7340 adopts a Type-II compensator circuit.

### **Programmed Current Control**

FAN7340 uses a Current-Mode control method. Current-Mode control loops: an outer feedback loop that senses output voltage (current) and delivers a DC control voltage to an inner feedback loop, which senses the peak current of the inductor and keeps it constant on a pulse-by-pulse basis. One of the advantages of the Current-Mode control is line/load regulation, which is corrected instantaneously against line voltage changes without the delay of an error amplifier.

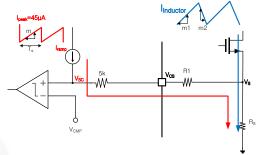

#### **Programmable Slope Compensation**

When the power converter operates in Continuous Conduction Mode (CCM), the current programmed controller is inherently unstable when duty is larger than 50%, regardless of the converter topology. The FAN7340 uses a Peak-Current-Mode control scheme with programmable slope compensation and includes an internal transconductance amplifier to accurately control the output current over all line and load conditions.

An internal  $R_{\text{slope}}$  resistor (5  $k\Omega)$  connected to sensing resistor  $R_{\text{S}}$  and an external resistor  $R_{\text{1}}$  can control the slope of  $V_{\text{SC}}$  for the slope compensation. Although the normal operating mode of the power converter is DCM, the boost converter operates in CCM in the case of rapid LED current increase. As a result, slope compensation circuit is an important feature.

The value of an external series resistor (R<sub>1</sub>) can be programmed by the user. In normal DCM operation, 5 k  $\Omega$  is recommended.

Figure 27. Slope Compensation Block Diagram

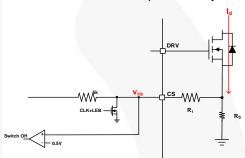

#### Cycle-by-Cycle Over-Current Protection

In boost topology, the switch can be damaged in abnormal conditions (inductor short, diode short, output short). It is always necessary to sense the switch current to protect against over-current failures. Switch failures due to excessive current can be prevented by limiting I<sub>d</sub>.

Figure 28. Cycle-by-Cycle OCP Circuit

When the voltage drops at  $R_1$  and  $R_S$  exceed a threshold of approximately 0.5 V, the power MOSFET over-current function is triggered after minimum turn-on time or LEB time (300 ns).

The peak voltage level at CS terminal:

$$V_{cs peak} = 45\mu \times (R_1 + R_s) \times DT_s + i_d \times R_s$$

(4)

Choose the boost switch current-sensing resistor (Rcs):

$$R_{CS} \ge \frac{0.25}{i_{L \text{ peak}}} \tag{5}$$

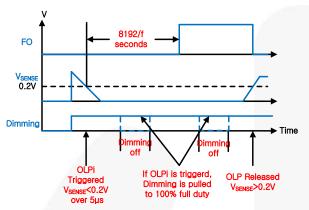

#### **Open-LED Protection (OLP)**

After the first PWM dimming-HIGH signal, the feedback sensing resistor (RSENSE) starts sensing the LED current. If the feedback voltage of the SENSE pin drops below 0.2 V, the OLP triggers to generate an error flag signal. Because OLP can be detected only in PWM dimming-HIGH; if OLP detecting time is over 5  $\mu s$ , PWM dimming signal is pulled HIGH internally regardless of external dimming signal. If OLP signal continues over blanking time, an error flag signal is triggered.

OLP blanking time is dependent on boost switch frequency per Equation (6). FAULT OUT signal is made through the FO pin, which needs to be connected 5 V reference voltage through a pull-up resistor. In normal operation, FO pin voltage is pulled down to ground. In OLP condition, FO pin voltage is pulled HIGH.

$$t_{d,olp} = 8192 / f_{OSC} [sec]$$

(6)

In system operation, OLP is triggered in only direct-short condition. Direct short means that some point of the LED string is shorted to set ground. In direct-short condition, the boost controller cannot control the LED current and a large current flows into the LED string directly from input power. To prevent this abnormal condition, the FO signal is used to turn off input power or the total system. FO signal is only triggered in OLP condition.

Figure 29. Open-LED Protection

In LED open load condition, OVP is triggered ahead of OLP.

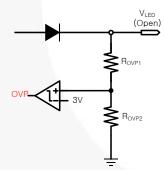

### **Over-Voltage Protection (OVP)**

Over-voltage protection is triggered when the voltage of the external output voltage trip point meets 3 V. After triggering OVP, the dimming switch and boost switch are turned off. The protection signal is recovered when the output voltage divider is below 2.9 V.

Figure 30. Over-Voltage Trip Point

Figure 31. OVP Trigger and Release

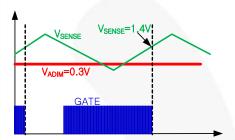

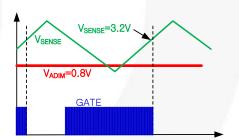

### **LED Over-Current Protection (OCP)**

The primary purpose of the over-current protection function is to protect the internal dimming MOSFET from excessive current. The OCP is triggered when the feedback voltage meets the clamping level (1.4 V  $\sim$  4 V) of the ADIM voltage x4. At 1  $\mu$ s delay after the OCP is triggered, the IC turns off both the boost FET and dimming FET and restarts the gate signal every tar automatically. tar can be calculated as:

$$\mathbf{t_{AR}} = 128 / f_{OSC} [sec] \tag{7}$$

- When V<sub>ADIM</sub>=0.3 V (V<sub>ADIM</sub>x4=1.2 V).

- 2. OCP threshold level is set to 1.4 V.

- 3. OCP is triggered at feedback voltage level = 1.4 V.

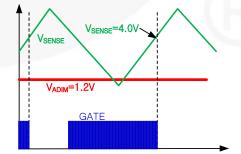

Figure 32. OCP Waveforms at V<sub>ADIM</sub>=0.3 V

- 1. When V<sub>ADIM</sub>=0.8 V (V<sub>ADIM</sub> x4=3.2 V).

- 2. OCP threshold level is set to 3.2 V.

- 3. OCP is triggered at V<sub>SENSE</sub> = 3.2 V.

Figure 33. OCP Waveforms at V<sub>ADIM</sub>=0.8 V

- 1. When V<sub>ADIM</sub>=1.2 V (V<sub>ADIM</sub> x4=4.8 V).

- 2. OCP threshold level is set to 4.0 V.

- 3. OCP is triggered at  $V_{SENSE} = 4.0 \text{ V}$ .

Figure 34. OCP Waveforms at V<sub>ADIM</sub>=1.2 V

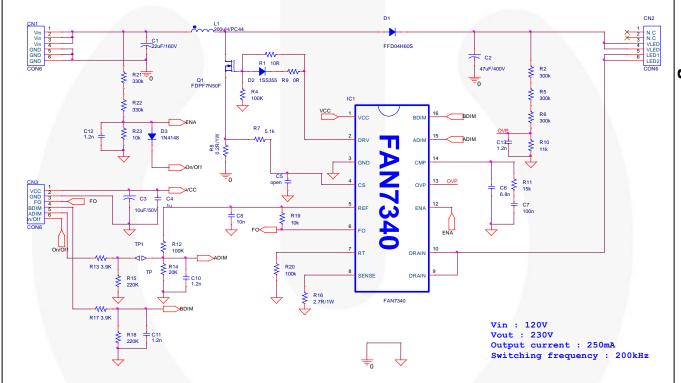

## **Typical Application Circuit (Boost Topology for LED Backlight)**

| Application      | Input Voltage Range      | Rated Output Power | Output current (Rated Voltage) | LED              |

|------------------|--------------------------|--------------------|--------------------------------|------------------|

| LED Backlight TV | 120 V <sub>DC</sub> ±10% |                    | 250 mA (230 V)                 | 72-LEDs/1-String |

#### **Features**

- High Efficiency

- Constant Current Boost Converters

- High-Voltage, High-Current LED Driving

## **Typical Application Circuit**

Figure 35. Typical Application Circuit

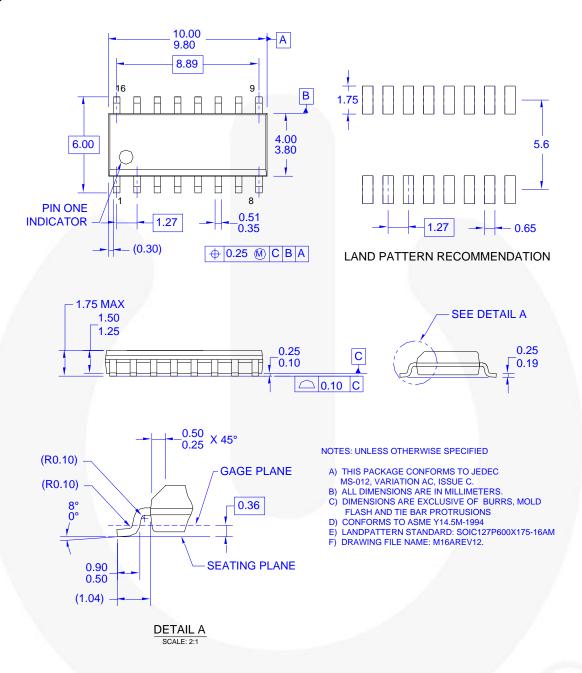

## **Physical Dimension**

Figure 36. 16-Lead, Small Outline Integrated Circuit (SOIC)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool<sup>TM</sup>

AccuPower<sup>TM</sup>

AX-CAP<sup>®</sup>\*

BitSiC<sup>TM</sup>

Build it Now<sup>TM</sup>

Core PLUS<sup>TM</sup>

Core POWER<sup>TM</sup>

CROSSVOL<sup>TTM</sup>

CTL<sup>TM</sup>

Current Transfer Logic<sup>TM</sup>

DEUXPEED<sup>®</sup>

Dual Cool<sup>TM</sup>

EcoSPARK<sup>®</sup>

Ecospark®

EfficientMax™

ESBC™

Fairchild®

Fairchild Semiconductor®

FACT Quiet Series™

FACT®

FAST®

FastvCore™

FETBench™

FPSTM

F-PFSTM

FRFET®

Global Power Resource®

GreenBridge™

Green FPSTM

Green FPSTM

Green FPSTM

G-BATTM

GTOTM

IntelliMAXTM

ISOPLANAR™

Making Small Speakers Sound Louder

and Better™

MegaBuck™

MICROCOUPLER™

MicroFET™

MicroPak™

MicroPak2™

MillerDrive™

MotionMax™

mWSaver™

OptoHiT™

OPTOLOGIC®

\_

PowerTrench®

PowerXS™

Programmable Active Droop™

QFET®

QS™

SignalWiseTM

SmartMaxTM

SMART STARTTM

Solutions for Your SuccessTM

SPM®

STEALTH™

SuperFET®

SuperSOT™.3

SuperSOT™.8

SuperSOT™.8

SupreMOS®

SyncFET™

Sync-Lock™

SYSTEM

GENERAL®

TinyBoost™

TinyBuck™

TinyCalc™

TinyLogic®

TINYOPTO™

TinyPower™

TinyPwM™

TinyWire™

TranSiC™

TriFault Detect™

TRUECURRENT®\*

µSerDes™

VSerDes"

UHC™

Ultra FRFET™

UniFET™

VCX™

VisualMax™

VoltagePlus™

XS™

OPTOPLANAR®

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN, NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |  |  |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev. 164

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.