1024-BIT(64-WORD BY 16-BIT)

ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

#### **DESCRIPTION**

The M6M80011AP, L, FP are 1024-bit (64-word x 16-bit) electrically erasable CMOS EEPROMs, and all have a built-in high voltage generator to enable operation in all modes by a single 5V power supply.

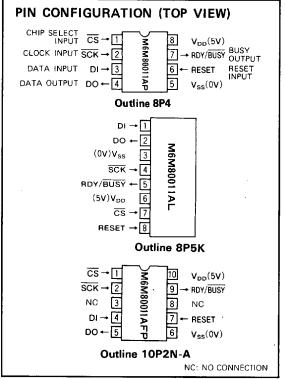

The difference between M6M80011AP, M6M80011AL and M6M80011AFP is only outline of package, and the following explanations are for M6M80011AP unless specifically indicated otherwise.

#### **FEATURES**

- Single 5V power supply

- Clock synchronous serial I/O

- Three ports control (CS and RESET, DI and DO can be interconnected.)

- Built-in sequential controller

- 100000 erase/write cycles

- 10 years data retention

#### **APPLICATION**

M6M80011A is especially suitable for use as a nonvolatile channel memory for electronic tuner and as the read only memory system that must be frequently reprogrammed in the field.

# 1024-BIT(64-WORD BY 16-BIT) ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

#### **FUNCTIONS**

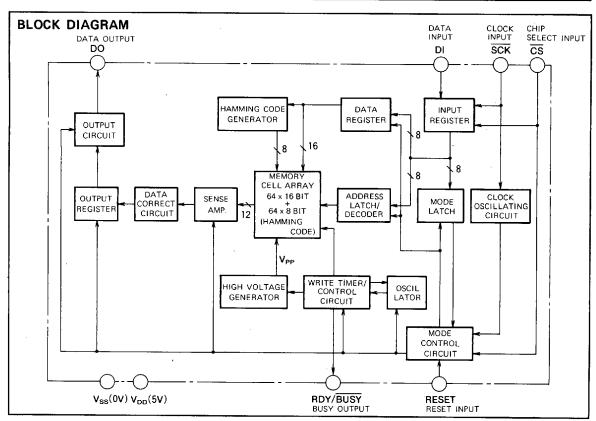

M6M80011AP is a clocked serial port compatible EEPROM, and data is input from the rising edge of clock signal and output by synchronizing to the falling edge of clock signal.

Data is grouped by 8 bits. The beginning 8 bits specify the mode, next 8 bits specify the address, and subsequent 16 bits specify the I/O data.

Any of five modes (write, read, write enable, write disable, status output) may be specified. The write time is set by an internal timer, and determination of whether write operation is in progress or not can be made from status of the RDY/BUSY pin or the DO pin status after the status mode has been set.

### PIN DESCRIPTION

| Pin           | Name              | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <del>cs</del> | Chip select input | <ol> <li>Chip selection is made by setting this pin to "L". When this port is "H", the internal sequential controller is reset. Therefore, this pin must be set to "H" before executing each mode.</li> <li>During the write operation (when BUSY output is "L"), write operation is continued regardless of the input to this pin.</li> <li>After write operation is finished, this pin must be set to "H" to make mode reading possible. In the case of "status output" mode only, reading is possible even if this pin is "L" after the sequential controller has been reset and tSTA has elapsed since the time when the write operation was started.</li> </ol> |

| SCK           | Clock input       | Input data is read at the rising edge of clock.     Data is output by synchronizing to the falling edge of clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DI            | Data input        | Data is input from this pin,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DO            | Data output       | Data is output from this pin, DI and DO can be interconnected,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RESET         | Reset input       | Must be set to "H" at the time of power ON or OFF.     When this pin is set to "H", the sequential controller and the write circuit are reset for memory protection. If this pin becomes "H" during write operation, the operation is halted.     This pin and CS can be interconnected. When this is done, CS (=RESET) must be held to "L" during write operation.                                                                                                                                                                                                                                                                                                  |

| RDY/BUSY      | Busy output       | <ul> <li>① This is "L" during write operation.</li> <li>② This is "L" at the time of power ON or OFF. In this condition, all inputs are disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## MODE FUNCTIONS

| Name          | Mode     | Address                                                                                      | Data                                                           | Functions                                 |  |

|---------------|----------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------|--|

| Read          | 10101000 | A <sub>0</sub> A <sub>1</sub> A <sub>2</sub> A <sub>3</sub> A <sub>4</sub> A <sub>5</sub> 00 | D <sub>0</sub> ~D <sub>7</sub> D <sub>8</sub> ~D <sub>15</sub> | Read from addresses $<$ $A_0 \sim A_5 >$  |  |

| Write         | 10100100 | A <sub>0</sub> A <sub>1</sub> A <sub>2</sub> A <sub>3</sub> A <sub>4</sub> A <sub>5</sub> 00 | D <sub>0</sub> ~D <sub>7</sub> D <sub>8</sub> ~D <sub>15</sub> | Write into addresses $<$ $A_0 \sim A_5 >$ |  |

| Write enable  | 10100011 | XXXXXXXX                                                                                     |                                                                | Write operation is enabled,               |  |

| Write disable | 10100000 | XXXXXXXX                                                                                     |                                                                | Write operation is disabled.              |  |

|               |          | 00xxxxx                                                                                      | 0 (Busy)                                                       | Busy flag                                 |  |

|               |          |                                                                                              | 1 (Ready)                                                      |                                           |  |

| Charles       | 10101001 | 10xxxxx                                                                                      | 0 (Enable)                                                     | Write enable flag                         |  |

| Status output | 10101001 |                                                                                              | 1 (Disable)                                                    |                                           |  |

|               |          | 011000000                                                                                    | 0 (Correct)                                                    | ECC flor                                  |  |

|               |          | 01XXXXXX                                                                                     | 1 (incorrect)                                                  | ECC flag                                  |  |

1024-BIT(64-WORD BY 16-BIT) ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

### STATUS OUTPUT MODE

### (1) Busy flag

The busy flag serves the same function as the  $\overline{\text{BUSY}}$  output pin.

When this flag is specified, "1" is output when ready from the 16 clock falling edge and "0" is output if busy (write operation in progress).

### (2) Write enable flag

M6M80011AP has a write enable flag, and write operation is executed only when this flag is "0". The contents of this flag can be updated only in the write enable (WEN) mode and the write disable (WDS) mode. The contents of this flag is underfined at the power on time, so that the WEN mode must be set before setting the write mode for write operation.

Once the WEN mode is set and this flag is set to the enable state, latch is in effect until the WDS mode is set. EEPROM can be read regardless of the status of this flag.

### (3) ECC flag

An ECC circuit, which corrects data errors, is built-in to insure high degree of memory cell reliability. The ECC circuit corrects data errors and outputs the corrected error if there is only one error each in the high-order 8 bits and the low-order 8 bits of 1 word (16 bits). When an error is corrected in at least one of the high-order or low-order byte, this flag is set to "1" to indicate that error correction has been made. The data is corrected in this case. When this flag is "0", it indicates that the correct data value was output without having to active the ECC circuit. By setting the ECC mode after the read mode, ECC information on the address that was specified immediately before can be varified

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter Test conditions |  | Ratings                   | Unit |

|------------------|---------------------------|--|---------------------------|------|

| $V_{DD}$         | Supply voltage            |  | -0.3~6.0                  | V    |

| V,               | Input voltage             |  | -0.3~V <sub>DD</sub> +0.3 | V    |

| V <sub>o</sub>   | Output voltage            |  | -0.3~V <sub>DD</sub> +0.3 | v    |

| lo <sub>H</sub>  | High-level output current |  | 0~10                      | mA   |

| loL              | Low-level output current  |  | 0~10                      | mA   |

| T <sub>stg</sub> | Storage temperature       |  | <b>−40~125</b>            | င    |

| Topr             | Operating temperature     |  | -10~70                    | r    |

## RECOMMENDED OPERATING CONDITIONS (Ta=-10~70°C, VDD=5V±10%, unless otherwise noted)

| Symbol   | Parameter                               |                    |     |                     |      |

|----------|-----------------------------------------|--------------------|-----|---------------------|------|

|          | 1 diameter                              | Min                | Nom | Max                 | Unit |

| $V_{DD}$ | Supply voltage                          | 4.5                | 5.0 | 5.5                 | ٧    |

| $V_{1H}$ | High-level input voltage DI             | 0.7V <sub>DD</sub> | Vop | V <sub>DD</sub>     | ٧    |

| VIH      | High-level input voltage RESET, CS, SCK | 0.8V <sub>DD</sub> | VDD | V <sub>DD</sub>     | V    |

| VIL      | Low-level input voltage DI              | 0                  | 0   | 0.3V <sub>DD</sub>  | ٧    |

| VIL      | Low-level input voltage RESET, CS, SCK  | 0                  | 0   | 0. 2V <sub>DD</sub> | V    |

## DC ELECTRICAL CHARACTERISTICS

| Symbol          | Parameter                               | Test conditions          |                    | Limits |                    |      |  |

|-----------------|-----------------------------------------|--------------------------|--------------------|--------|--------------------|------|--|

|                 |                                         |                          | Min                | Тур    | Max                | Unit |  |

| V <sub>DD</sub> | Supply voltage                          |                          | 4.5                | 5.0    | 5.5                | V    |  |

| l <sub>DD</sub> | Supply current                          | V <sub>DD</sub> =5.5V    |                    | 5      | 8                  | mA   |  |

| V <sub>IH</sub> | High-level input voltage DI             |                          | 0.7V <sub>DD</sub> |        | V <sub>DD</sub>    |      |  |

| V <sub>IH</sub> | High-level input voltage RESET, CS, SCK |                          | 0.8V <sub>DD</sub> |        | V <sub>DD</sub>    | V    |  |

| VIL             | Low-level input voltage DI              |                          | 0                  |        | 0.3V <sub>DD</sub> | v    |  |

| VIL             | Low-level input voltage RESET, CS, SCK  |                          | 0                  |        | 0.2V <sub>DD</sub> | v    |  |

| V <sub>OH</sub> | High-level output voltage               | I <sub>OH</sub> =-400 µA | 2.4                |        | 1                  | v    |  |

| VoL             | Low-level output voltage                | I <sub>O1</sub> =2.1mA   |                    |        | 0.4                | v    |  |

## 1024-BIT(64-WORD BY 16-BIT) ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

## AC ELECTRICAL CHARACTERISTICS

|                           | Parameter                                                                         | Test conditions | Limits . |     |     | Unit  |

|---------------------------|-----------------------------------------------------------------------------------|-----------------|----------|-----|-----|-------|

| Symbol                    |                                                                                   |                 | Min      | Тур | Max | Offic |

| t <sub>wH</sub>           | Positive data shift clock pulse width                                             |                 | 450      |     |     | ns    |

| twL                       | Negative clock pulse width                                                        |                 | 450      |     |     | ns    |

| t <sub>ww+</sub>          | Clock hold time (every 8 clocks)                                                  |                 | 4        |     |     | μS    |

| t <sub>su(CS-SCK)</sub>   | Chip select set up time before the fall of the clock                              |                 | 1        |     |     | μS    |

| th(sck-cs)                | Chip select hold time after the rise of the clock                                 |                 | 4        |     |     | μS    |

| t <sub>su(DI-SCK)</sub>   | Data set up time before the rise of the clock                                     |                 | 150      |     |     | ns    |

| th(SCK-DI)                | Data hold time after the rise of the clock                                        |                 | 200      |     |     | ns    |

| tsu(sck-cs)               | Clock set up time before the fall of the chip select                              |                 | 1        |     |     | μ\$   |

| th(cs-sck)                | Clock hold time after the rise of the chip select                                 |                 | 1        |     |     | μ\$   |

| t <sub>PD</sub>           | Data delay time after the fall of the clock                                       |                 |          |     | 350 | ns    |

| tov                       | Data valid time after the rise of the chip select                                 |                 |          |     | 1   | μδ    |

| t <sub>E/W</sub>          | Self-time write sequence time                                                     |                 |          |     | 15  | ms    |

| t <sub>CSH</sub>          | Positive chip select width                                                        |                 | 4.       |     |     | μS    |

| thw                       | Chip select, clock hold time after the start of the write sequence                |                 | 4        |     |     | μs    |

| t <sub>STA</sub> (Note 1) | At setting status mode, clock hold time start of the write sequence when CS is 0. |                 | 12       |     |     | μs    |

Note 1. t<sub>STA</sub> indicates the maximum value of the sequential controller reset pulse that is generated after the write operation is started. When the sequential controller is reset, only the status output can be read.

## **NONVOLATILE CHARACTERISTICS**

| Symbol | Parameter                  | Test conditions       |     | 1.1-14- |     |        |

|--------|----------------------------|-----------------------|-----|---------|-----|--------|

|        |                            |                       | Min | Тур     | Max | Units  |

| NEW    | Erase/Write cycle per word |                       | 105 |         |     | cycles |

| ts     | Data retention             | N <sub>EW</sub> = 105 | 10  |         |     | years  |

# 1024-BIT(64-WORD BY 16-BIT) ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

### **TIMING DIAGRAMS**

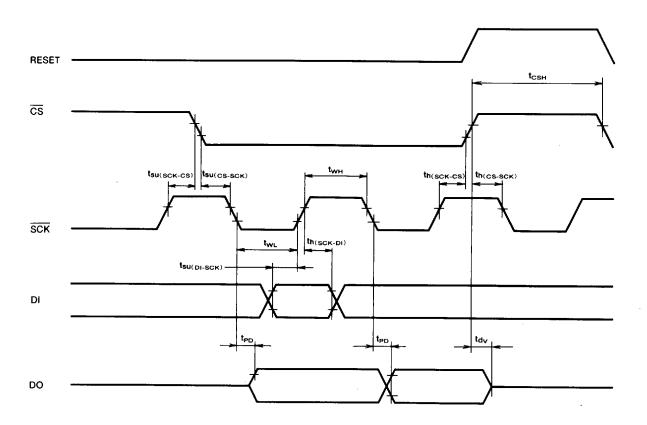

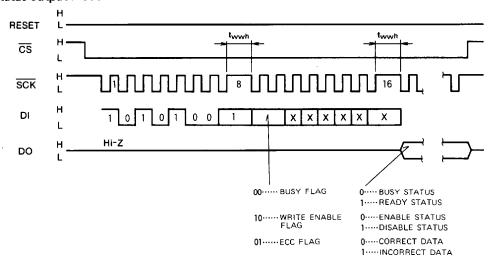

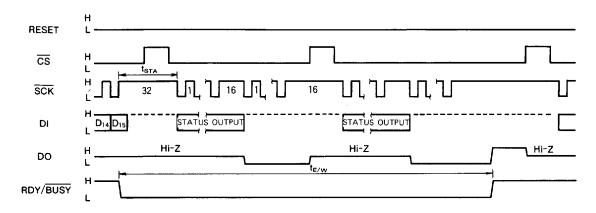

## (1) Synchronizing data I/O timing

Fig. 1 Synchronizing timing

## (2) SCK "H" hold time at every 8 clocks

The timing pattern shown above is maintained during transfer of 8-bit data, but the clock "H" hold time  $t_{wwh}$  is necessary at every 8th clock for  $\overline{SCK}$  input in all modes.

1024-BIT(64-WORD BY 16-BIT)

ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

## **TIMING CHART for VARIOUS MODES**

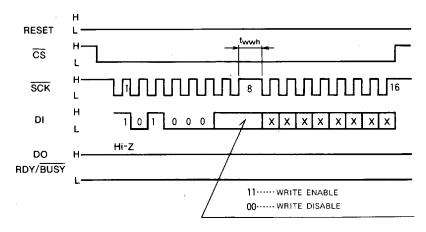

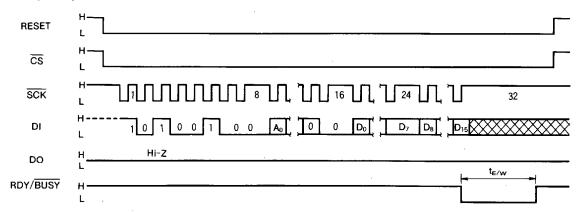

- (1) When controlling CS and RESET pins

- Write enable and write disable mode

Fig. 2 Sequence at write enable and write disable modes

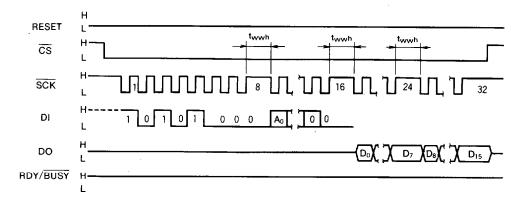

### • Status output mode

Fig. 3 Sequence at status output mode

The status of each status flag specified from the DO pin is output starting at the rising edge of the 16th clock. Output is not dependent on clock but continues until  $\overline{\text{CS}}$  becomes "H".

# 1024-BIT(64-WORD BY 16-BIT) ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

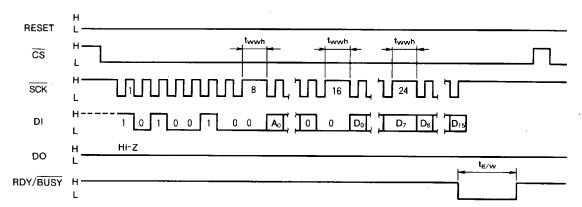

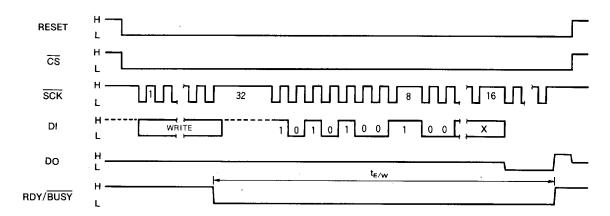

#### Read mode

Fig. 4 Sequence at read mode

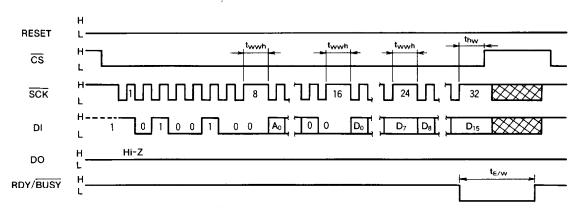

### Write mode

Fig. 5 Sequence at write mode

Execution of the write operation starts at the rising edge of the 32nd clock.

During the write operation, the  $\overline{CS}$  input value may be either "H" or "L". If the  $\overline{CS}$  pin is held to "L" during the write operation, the read operation is possible only in the status mode.

Thus, the  $\overline{\text{SCK}}$  is to be used for other tasks during the

write operation,  $\overline{CS}$  should be set to "H" as shown in Figure 6 (even is  $\overline{CS}$  is held to "L",  $\overline{SCK}$  can be used by other tasks if a dummy bit input is performed as shown in Figure 10).

To read next mode after  $t_{\text{E/W}},\,\overline{\text{CS}}$  must be set to "H" first.

# 1024-BIT(64-WORD BY 16-BIT) ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

Fig. 6 Sequence at write mode

To use  $\overline{SCK}$  and DI for other tasks during the write operation,  $\overline{CS}$  must be set to "H" after  $t_{hw}$  has elapsed from the rising edge of the 32nd clock as shown in Figure 6.

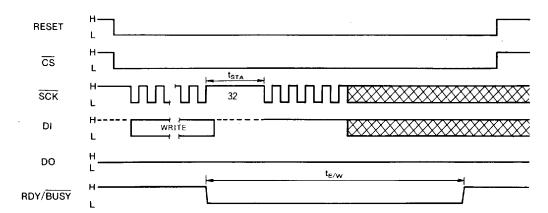

Fig. 7 Sequence of status output (busy flag) during the write operation

After write operation has started, the sequential controller is reset automatically, so read operation in the status mode become possible only after  $t_{STA}$  has elapsed from the time the write operation started without having to set  $\overline{CS}$  to "H".

Before the status mode is set again,  $\overline{\text{CS}}$  must be set to "H" as in the ordinary mode setting procedure.

## 1024-BIT(64-WORD BY 16-BIT) ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

## (2) When connecting between CS and RESET pins

### • Write mode

Fig. 8 Sequence of write operation

During the write operation, the  $\overline{\text{CS}}\text{--RESET}$  pin must be set to "L".

Because the read operation is possible only in the status mode once the write operation starts as described above, SCK must be held to "H" when not setting the status mode. For using SCK and DI for other tasks during the write operation, see Figure. 10.

Fig. 9 Sequence of status output during write operation

The read operation in the status mode becomes possible after  $t_{STA}$  has elapsed from the time the write operation started. Attention is called to the fact, when the status mode is set, the DO pin is in the output state until  $\overline{CS}$  is set to "H".

## 1024-BIT(64-WORD BY 16-BIT) ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM

Fig. 10 Sequence of write operation

As shown in Figure 9, the read operation in the status mode becomes possible after  $t_{STA}$  has elapsed from the time the write operation started, and the DO pin is set to the output state when the status mode is set. When using the DO pin is addition to the  $\overline{SCK}$  and DI pins for other tasks, a dummy bit input must be made after  $t_{STA}$  has elapsed from the time the write operation started to avoid the status mode before executing the other tasks.

Other (than dummy bit) data input is equally effective for this purpose as long as it does not generate the status mode instruction code (10101001).