# Pira,cz

# **Basic Radio Data System Encoder MCU**

#### DESCRIPTION

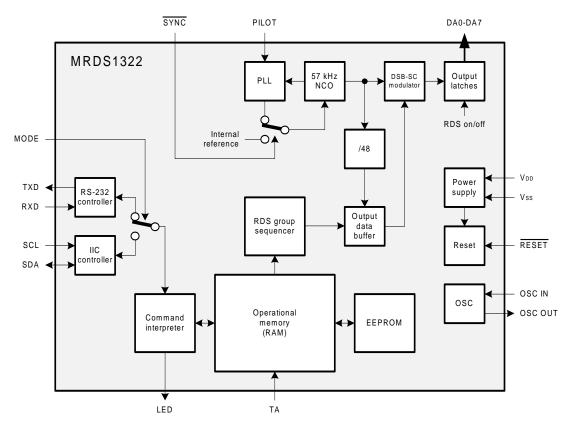

The MRDS1322 is a complete Radio Data System (RDS) encoder, configured via local onboard RS232 or I<sup>2</sup>C bus. It implements physical and datalink layers and supports basic set of RDS services.

Internally the device is based on a programmable microcontroller. With a minimum of external parts it forms a simple RDS encoder add-on to analogue FM broadcast designs.

## **RDS SERVICES DIRECTLY SUPPORTED**

- Ы **Program Identification**

- PS Program Service

- PTY Program Type

- TP Traffic Program

- Alternative Frequencies AF

- Traffic Announcement . TA

- DI Decoder Identification

- M/S Music/Speech

- Radiotext RT

- **UDG** User defined groups (2 modes)

#### CAPACITY

- AF: up to 15 items

- RT: 64 characters

- Dynamic PS text: up to 80 characters

- UDG: 2 groups (1 for each mode)

#### **FEATURES**

- Single supply 1.8 to 5.5 V

- Typical operating current: 7.9 mA @ 5.0 V 5.6 mA @ 3.3 V

- Minimum external parts

- Industrial temperature range

- Internal EEPROM memory for data storage . during power-off

- Support for external TA switch

- Indication LED output

- Both stereo and mono operation possible Digital 19 kHz pilot tone PLL with software

- phase shift adjustment Parallel 8-bit D/A converter, 361 kHz sampling

- rate (over-sampled)

- Broadcast quality output signal

- Only simple output filter required RDS/RBDS signal:

- conforms to CENELEC EN 50067 / EN 62106

- Continuous RDS transmission during all operations

- Communication bus for configuration purposes: Selectable RS232 or I<sup>2</sup>C unidirectional or bi-directional operations

- RS232 baudrate: 2400 or 19200 Bd

- I<sup>2</sup>C bus speed: DC to 400 kHz Selectable polarity of RS232 signal

- Buffered PS and UDG data

- 4 modes for dynamic/scrolling PS incl. word alignment and one-by-one character scrolling

- Powerful Windows control software available

- **RoHS** compliant

- Packages available: 20-lead PDIP 20-lead SOIC

20-lead SSOP

# APPLICATIONS

- Extremely low-cost FM broadcast RDS encoders

- Small all-in-one FM transmitters

- Private messaging systems

- RDS encoders for cable FM modulators

- Text output from any device to FM receiver

The manufacturer is not liable for any damages, including but not limited to, lost profits, lost savings, or other incidental or consequential damages arising out of the use of this product.

No part of this datasheet may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording or information storage and retrieval systems, for any purpose other than the purchaser's personal use.

Information in this document is subject to change without notice.

Revision 2020-07-24

# TABLE OF CONTENTS

| 1 | Pi                                                                | in Diagrams and Description                                                                                                                                                                                    | . 3                                           |

|---|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2 | <b>EI</b><br>2.1                                                  | lectrical Characteristics<br>Related Documents and Development Support                                                                                                                                         |                                               |

| 3 | Ca<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8        | onnection Diagrams and Application Notes<br>Device reset<br>Crystal oscillator<br>Power supply<br>Internal PLL<br>External TA switch<br>Operation LED<br>Digital-to-Analog converter<br>Output low-pass filter | . 7<br>. 7<br>. 7<br>. 7<br>. 7<br>. 7<br>. 8 |

| 4 | <b>C</b><br>4.1                                                   | ommunication Mode Selection<br>Interfacing the MRDS1322                                                                                                                                                        |                                               |

| 5 | l <sup>2</sup> (<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | C Communication (MODE 3)<br>Bus specification<br>Write operations<br>Read operations<br>Control byte<br>Acknowledge<br>Clock stretching.<br>Application example (setting PTY)                                  | 10<br>10<br>10<br>11<br>11<br>11              |

| 6 | R<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                              | S232 Communication (MODE 0, 1, 2)<br>Write operations<br>Read operations<br>Byte stuffing<br>Application example (setting PI to 30FF and reading it back for verify)<br>Firmware update                        | 12<br>12<br>12<br>12                          |

| 7 | C                                                                 | ommented Memory Map                                                                                                                                                                                            | 13                                            |

| 8 | 8.1<br>8.2<br>8.3                                                 | est Circuit                                                                                                                                                                                                    | 17<br>17<br>18                                |

| 9 | Pa                                                                | ackage Details                                                                                                                                                                                                 | 19                                            |

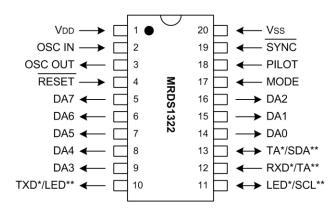

# 1 PIN DIAGRAMS AND DESCRIPTION

\* Valid for RS232 mode / \*\* valid for  $I^2C$  mode.

| Pin name        | Description                                                                                                                                                                                                                                                                                                                                                                                        | Internal<br>weak pull-up |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| /RESET          | <b>Device reset</b><br>Logical low on this pin holds the device in reset state.<br>If the reset function is not required, connect this pin to $V_{DD}$ through a resistor.                                                                                                                                                                                                                         |                          |

| /SYNC           | <b>Pilot sync. switch</b><br>Drive this pin low to confirm the pilot tone validity and to enable internal pilot PLL assuring stable phase relation between pilot tone and RDS sub-carrier.<br>If the pilot sync. function is not required (mono or low power broadcast), leave this pin unconnected or connect it to V <sub>DD</sub> through a resistor, so internal clock reference will be used. | *                        |

| PILOT           | <b>Pilot tone input</b><br>Optional 19 kHz pilot tone input for the synchronization purpose.<br>If pilot tone is not available or does not meet the specifications<br>required, the /SYNC pin should be driven high.                                                                                                                                                                               |                          |

| ТА              | <b>TA switch</b><br>RDS Traffic Announcement (TA) flag control.<br>If the TA external switching function is not required, leave this pin<br>unconnected.                                                                                                                                                                                                                                           | ✓                        |

| V <sub>DD</sub> | <b>Positive supply</b><br>Apply $V_{DD}$ power supply voltage to this pin.<br>Decoupling capacitor is required on $V_{DD}$ and $V_{SS}$ pins. A 100 nF 10-<br>50V ceramic capacitor is recommended. The decoupling capacitor<br>should be placed as close to the pins as possible.                                                                                                                 |                          |

| V <sub>SS</sub> | Ground reference                                                                                                                                                                                                                                                                                                                                                                                   |                          |

| OSC IN  | Crystal oscillator input<br>Tie to 4.332 MHz crystal pin.                                                                                                                                                                           |   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| OSC OUT | <b>Crystal oscillator output</b><br>Tie to 4.332 MHz crystal pin.<br>Can be used for clocking another device on the board.                                                                                                          |   |

| LED     | <b>Operation LED</b><br>Connect an indication LED (+) through a resistor or leave<br>unconnected.                                                                                                                                   |   |

| MODE    | <b>Communication mode</b><br>The MODE pin selects the communication mode. This pin is read by<br>the device on power-up or after reset. Thus the MODE selection will<br>not take effect until the next reset or power off-on cycle. | ~ |

| SCL     | I <sup>2</sup> C serial clock output<br>Open-drain terminal, external 2k pull-up resistor is required.                                                                                                                              |   |

| SDA     | I <sup>2</sup> C serial data input/output<br>Open-drain terminal, external 2k pull-up resistor is required.                                                                                                                         |   |

| тхр     | <b>Serial port transmit data</b><br>Serial RS-232 port transmit data output. Baud rate and signal polarity<br>is selectable via the pin MODE.                                                                                       |   |

| RXD     | <b>Serial port receive data</b><br>Serial RS-232 port receive data input. Baud rate and signal polarity is<br>selectable via the pin MODE.                                                                                          |   |

| DA0-DA7 | <b>D/A Converter bit 0 to 7</b><br>These pins together form a driving signal for the parallel D/A converter.                                                                                                                        |   |

Figure 1.1 – Internal logical structure (simplified)

# 2 ELECTRICAL CHARACTERISTICS

## Maximum Ratings

| $\begin{array}{l} \mbox{Ambient temperature under bias.} \\ \mbox{Storage temperature.} \\ \mbox{Voltage on V}_{DD} \mbox{ with respect to V}_{SS} \\ \mbox{Voltage on any I/O pin with respect to V}_{SS} \\ \mbox{Voltage on any I/O pin with respect to V}_{SS} \\ \mbox{Maximum current sourced by any output pin} \\ \mbox{Maximum current sunk by any output pin} \\ Maximum current$ | 65 °C to +150 °C<br>0.3 V to +6.0 V<br>3 V to (V <sub>DD</sub> + 0.3 V)<br>25 mA |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Maximum current sunk by any output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 mA                                                                            |

Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device.

| Symbol                           | Parameter                                | Min.    | Тур.  | Max.                              | Unit  | Conditions                        |

|----------------------------------|------------------------------------------|---------|-------|-----------------------------------|-------|-----------------------------------|

| V <sub>DD</sub>                  | Supply voltage                           | 1.8     | -     | 5.5                               | V     |                                   |

| ED                               | EEPROM Endurance                         | -       | 1M    | -                                 | E/W   | -40 °C to +85 °C                  |

| Fosc                             | Oscillator Frequency                     | -0.01 % | 4.332 | +0.01 %                           | MHz   | * Note 1                          |

| Fs                               | D/A Converter sampling rate              | -       | 361   | -                                 | kHz   |                                   |

| L <sub>PILOT</sub>               | Pilot tone level                         | 150     | -     | V <sub>DD</sub> - V <sub>SS</sub> | mV pp | Stereo transmission               |

| B <sub>PLL</sub>                 | PLL capture range                        | -       | 8     | -                                 | Hz    |                                   |

| - <b>-</b>                       | Power-up delay                           |         | -     | 1100                              | ms    | Mode 0, 1, 2                      |

| T <sub>PU</sub>                  |                                          | -       |       | 140                               |       | Mode 3                            |

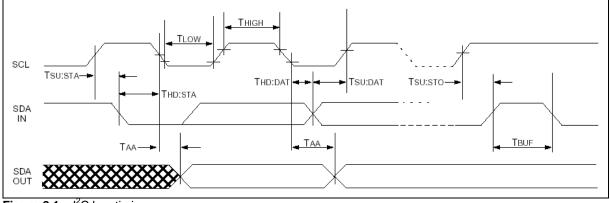

| F                                | I <sup>2</sup> C clock frequency         | 0       | -     | 400                               | kHz   | Master supports clock stretching. |

| F <sub>CLK</sub>                 |                                          |         |       | 20                                |       | Master ignores clock stretching.  |

| T <sub>HIGH</sub>                | I <sup>2</sup> C clock high time         | 600     | -     | -                                 | ns    |                                   |

| T <sub>LOW</sub>                 | I <sup>2</sup> C clock low time          | 1300    | -     | -                                 | ns    |                                   |

| T <sub>HD</sub> /T <sub>SU</sub> | I <sup>2</sup> C hold/setup time         | 600     | -     | -                                 | ns    |                                   |

| T <sub>HD:DAT</sub>              | I <sup>2</sup> C data input hold time    | 0       | -     | -                                 | ns    |                                   |

| T <sub>SU:DAT</sub>              | I <sup>2</sup> C data input setup time   | 100     | -     | -                                 | ns    |                                   |

| T <sub>AA</sub>                  | I <sup>2</sup> C output valid from clock | -       | -     | 3500                              | ns    |                                   |

| Τ                                | I <sup>2</sup> C bus free time           | 2400    | -     | -                                 | μs    |                                   |

| T <sub>BUF</sub>                 |                                          | 1000    | -     | -                                 | ms    | EEPROM store cmd.                 |

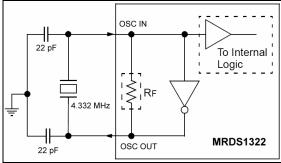

\* Note 1:

The crystal must oscillate on 4.332 MHz with tolerance of +/- 0.01 %. Depending on the crystal characteristics, the parallel capacitors (see section 3.2) may require change of their value for entire production batch. This should be tested on a sample before mass assembly.

The crystal frequency offset can be also read by a counter on the MRDS1322 pin 5 with the /SYNC pin left unconnected. The frequency read must be 57 kHz +/- 6 Hz.

Recommended crystal type is Auris Q- 4,332000M-HC49US-F-30-30-D-16 or equivalent.

# Supply Current (25 °C)

| Supply voltage | 2.0 V  | 3.3 V  | 5.0 V  |

|----------------|--------|--------|--------|

| Operating      | 3.6 mA | 5.6 mA | 7.9 mA |

| Subcarrier off | 2.0 mA | 3.7 mA | 4.0 mA |

| Held in Reset  | 0.5 mA | 0.9 mA | 1.1 mA |

# 2.1 <u>Related Documents, Software and Development Support</u>

Technical support is available through the web site at: http://pira.cz/rds/

The web site contains the following information: data sheets, application notes, sample programs, design resources, user's guides, latest software releases incl. Windows control software (TinyRDS, Magic RDS 4), Frequently Asked Questions (FAQ), online shop, online forum.

The most important links are listed below:

- FAQ: http://pira.cz/rds/show.asp?art=rds\_encoder\_support

- MicroRDS encoder & Windows control software: http://pira.cz/rds/show.asp?art=micrords\_encoder

- MicroRDS Encoder User Guide: http://pira.cz/rds/micrords.pdf

- Software development resource: http://pira.cz/rds/show.asp?art=micrords\_development

- Pira.cz online shop: http://pira.cz/shop/

The MicroRDS encoder is based on the MRDS1322 chip. It is a sample design which implements everything needed to experience the MRDS1322 device.

## 3 CONNECTION DIAGRAMS AND APPLICATION NOTES

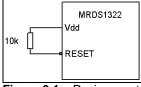

#### 3.1 Device reset

A reset is generated by holding the /RESET pin low. The device has a noise filter in the reset path which detects and ignores small pulses.

A reset pulse is generated on-chip whenever  $V_{\text{DD}}$  rises above a certain threshold. This allows the device to start in the initialized state when  $V_{\text{DD}}$  is adequate for operation.

To take advantage of this feature, tie the /RESET pin through a resistor (1k to 10k) to  $V_{DD}$ . This will eliminate external RC components usually needed to create a reset delay.

Figure 3.1 – Device reset.

When the device starts normal operation (i.e., exits the reset condition), device operating parameters (voltage, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

## 3.2 Crystal oscillator

Figure 3.2 – Crystal oscillator.

## 3.3 Power supply

The power supply must be bypassed close to the device with a 100 nF ceramic capacitor. The device can operate within wide power supply voltage range (see the Electrical Specifications). The output RDS level varies proportionally to the supply voltage.

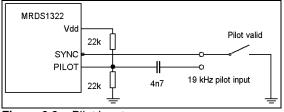

# 3.4 Internal PLL

The MRDS1322 includes an internal phase locked loop, which synchronises the RDS subcarrier with

19 kHz pilot tone in case of stereo broadcast. Parameters of the PLL are controlled by software.

Pilot tone is tied to the PILOT input pin. This pin includes an internal comparator with a threshold voltage of  $V_{DD}/2$ . Thus a pilot in TTL levels may be connected directly. For sine wave the DC component must be fixed at  $V_{DD}/2$  using two resistors and coupling capacitor (figure 3.3).

The PLL is active if the /SYNC pin is driven low. This configuration makes easy to connect commonly available clock recovery circuits (LM567) if the pilot tone needs to be filtered from MPX signal.

The PLL should be permanently disabled (in case of mono transmission or if that function is not required) by leaving the /SYNC pin unconnected or connecting it to  $V_{DD}$  (directly or through a resistor).

Figure 3.3 – Pilot input.

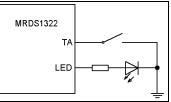

# 3.5 External TA switch

The external TA switch can set the Traffic Announcement flag to 1 if TP flag is on (1). The TA flag is set to 1 if the TA input is driven low. This can be done using simple mechanical switch (figure 3.4) or any logic circuit.

Where the external TA switch feature is not required, the TA pin may be left unconnected.

Figure 3.4 – TA and LED connection.

## 3.6 Operation LED

The LED indicates that the device is in operation. It blinks approx. once per second. It also indicates that data are being received through the communication interface (RS232 or  $I^2C$  bus).

#### 3.7 Digital-to-Analog converter

The MRDS1322 uses parallel 8-bit D/A converter with over-sampling technique to generate the RDS signal modulated at 57 kHz subcarrier. Digital data provided on DAx pins can be directly formed into analogue output signal using an extremely low-cost resistor network.

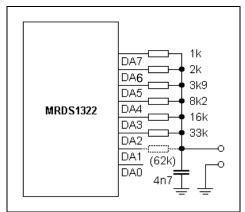

Figure 3.7 shows a simple 6-bit D/A converter using six of binary weighted resistors. It contains one resistor for each bit of the DAC connected to a summing point. It's possible to add seventh resistor (62k) and form a 7-bit DAC.

Figure 3.7 – 6 (or 7) -bit D/A converter network.

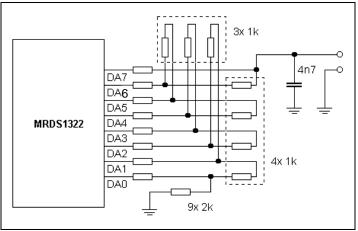

Figure 3.8 shows accurate 8-bit DAC using R/2R resistor network. It's a binary weighted DAC that creates each value with a repeating structure of 2 resistor values, R and R times two. This is an optimal DAC for this device.

Figure 3.8 – 8-bit D/A converter R/2R network.

Below is a table showing typical values accomplished with each DAC type. The values are measured in baseband on FM transmitter input. 0 dBc corresponds to the RDS signal main spectral component at 57 kHz. 0 dB corresponds to 75 kHz peak FM deviation; peak deviation caused by RDS: 3.4 kHz.

| Parameter                      | 6-bit                | 7-bit                | 8-bit R/2R           |

|--------------------------------|----------------------|----------------------|----------------------|

| 57 kHz output signal bandwidth | +/- 2.4 kHz (43 dBc) | +/- 2.4 kHz (45 dBc) | +/- 2.4 kHz (50 dBc) |

| Spurious suppression           | > 74 dB              | > 80 dB              | > 90 dB              |

Note: Typical signal-to-noise ratio of FM broadcast transmitters is 70 – 80 dB.

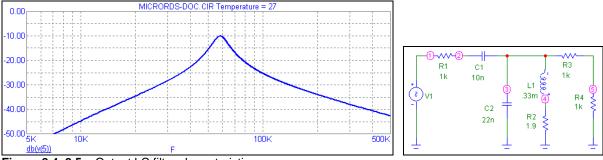

#### 3.8 Output low-pass filter

The output RDS signal modulated at 57 kHz subcarrier requires no special filtering. Spurious products are kept below -70 dB broadcast limit and the D/A conversion residues around the sampling frequency can be cut-off using any simple low-pass filter. This may be based either on active filter or a simple LC element. For FM broadcast purposes the low-pass filter rejection should be at least 20 dBc on the sampling frequency. It is recommended for high quality FM broadcasting that the output filter characteristics interpolate at least these values:

| 15 kHz  | 57 kHz | 360 kHz |

|---------|--------|---------|

| -20 dBc | 0 dBc  | -30 dBc |

## 4 COMMUNICATION MODE SELECTION

The device supports various communication modes for RDS data configuration. These modes cover all common methods of control including interfacing with mcu's, PC serial ports, USB adapters, Ethernet adapters, modems, etc. The communication protocol does not contain any security mechanism. If it is needed in your application, it must be assured by an upper layer.

The MODE pin selects the communication mode. This pin is read by the device on power-up or after reset. Some pins have different function, depending on the MODE selection (see section 1).

| Mode No. | Description                       | Selection                                                                 |

|----------|-----------------------------------|---------------------------------------------------------------------------|

| 0        | RS232, 19200 Bd, active low (TTL) | Leave the MODE pin unconnected or connect it to V <sub>DD</sub><br>MODE o |

| 1        | RS232, 19200 Bd, active high      | Connect the MODE pin to DA2 pin through a diode<br>MODE o                 |

| 2        | RS232, 2400 Bd, active low (TTL)  | Connect the MODE pin to DA1 pin through a diode<br>MODE o                 |

| 3        | I <sup>2</sup> C Slave            | Connect the MODE pin to V <sub>SS</sub><br>MODE o                         |

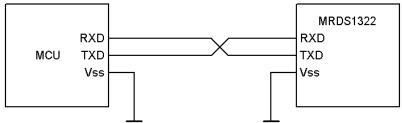

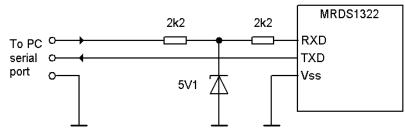

## 4.1 Interfacing the MRDS1322

Figure 4.1 – Interfacing the MRDS1322 in mode 0 or 2.

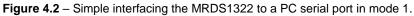

**Figure 4.3** – Interfacing the MRDS1322 in mode 3.

# 5 I<sup>2</sup>C COMMUNICATION (MODE 3)

## 5.1 Bus specification

The  $I^2C$  is a bi-directional bus used to transfer addresses and data into and out of the device. According to the bus specification the MRDS1322 is a slave device driven by master. The master generates clock signal, START/STOP conditions, addresses and specifies if read or write operation will be performed. All devices on the  $I^2C$  bus are open drain terminals, therefore the bus requires pull-up resistors to  $V_{DD}$ .

The  $l^2C$  peripheral implemented in the MRDS1322 fully meets the  $l^2C$  specification with respect to the bus timing specified in section 2. The application developer may apply the same routines and libraries like for the communication with standard serial  $l^2C$  EEPROM's (for example 24LC04). Configuration of the RDS transmission is made by writing values to address locations as showed in section 7.

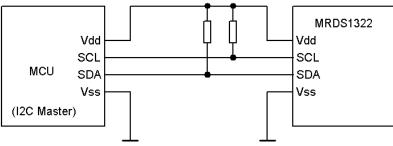

## 5.2 Write operations

All write operations are performed in RAM so the number of write operations is unlimited. Storing the data into internal EEPROM memory is activated by a special command – writing a special value to the CONTROL register. Number of bytes written in page write mode is limited only by access RAM boundaries. For safety purposes the internal address counter will not wrap around if the last byte accessible is overstepped.

Figure 5.2 – Page write

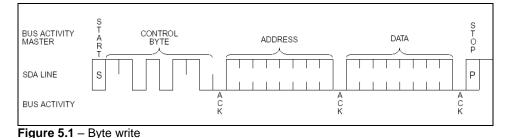

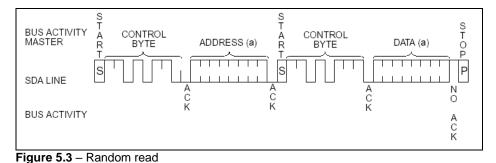

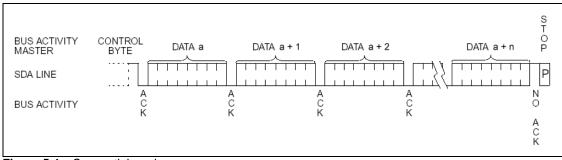

## 5.3 Read operations

Read operations allow the master to access any RAM location. Implementation of the read operations is optional. To perform the read operation, first the word address must be set. This is done by sending the word address to the device as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the R/W bit set to a one.

Figure 5.4 – Sequential read

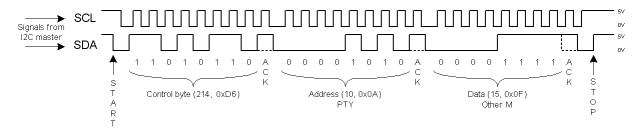

#### 5.4 Control byte

A control byte is the first byte received following the start condition from the master device. The control byte consists of a 7-bit control code. For the MRDS1322 this is set as 1101011 binary for read and write operations. The last bit of the control byte defines the operation to be performed. When set to one a read operation is selected, when set to zero a write operation is selected.

| Operation | Control byte |     |  |  |  |

|-----------|--------------|-----|--|--|--|

| Operation | Control code | R/W |  |  |  |

| Write     | 1101011      | 0   |  |  |  |

| Read      | 1101011      | 1   |  |  |  |

#### 5.5 Acknowledge

Each receiving device, when addressed, is obliged to generate an acknowledge (ACK) after the reception of each byte (9th bit). The master device must generate an extra clock pulse which is associated with this acknowledge bit. The device that acknowledges, has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

#### 5.6 Clock stretching

A slave causes the SCL pin to be held low at the end of each data receive sequence. By holding the SCL line low, the slave has a time to process the last byte received before the master initiates another data transfer sequence. This enables the master to use high SCL frequency and prevents data lost due to possible overrun in the slave.

#### 5.7 Application example (setting PTY)

## More about I<sup>2</sup>C:

[1] - The I<sup>2</sup>C Bus Specification; Philips Semiconductors, www.nxp.com

[2] – 24LC04B/08B I<sup>2</sup>C Serial EEPROM's datasheet; Microchip, www.microchip.com

## 6 RS232 COMMUNICATION (MODE 0, 1, 2)

For the RS232 communication, any write or read command as well as the data read comprise of a series of bytes, delimited by two reserved bytes (start byte and stop byte), which mark the beginning and end of the block. The start and stop bytes are uniquely defined, and may not occur within the block. In order to prevent this, the data is byte-stuffed prior to transmission. Byte-stuffing transforms an illegal occurrence of a reserved byte into two legal bytes. The reverse process is applied at read operation, byte-stuffed data are converted prior to processing. Thus, although the start and stop bytes are reserved, the data may contain bytes with any value.

### 6.1 Write operations

Each write command contains a start address pointing to the first location written in the device memory. No response is sent back. Thus the TXD pin may be left unconnected.

| Start byte<br>0xFE                            | Start<br>address | Data | Stop byte<br>0xFF |  |  |

|-----------------------------------------------|------------------|------|-------------------|--|--|

| <b>Figure 4.4</b> $M/rite compare and formed$ |                  |      |                   |  |  |

Figure 4.1 – Write command format

#### 6.2 Read operations

Each read command contains a read constant (0xD0), start address pointing to the first location read and length of the data read.

| Start byte<br><b>0xFE</b> | Read<br>constant<br><b>0xD0</b> | Start<br>address | Length | Stop byte<br>0xFF |  |

|---------------------------|---------------------------------|------------------|--------|-------------------|--|

|---------------------------|---------------------------------|------------------|--------|-------------------|--|

Figure 4.2 – Read command format

|  | Start byte<br>0xFE | Start<br>address | Data | Stop byte<br>0xFF |

|--|--------------------|------------------|------|-------------------|

|--|--------------------|------------------|------|-------------------|

Figure 4.3 – Response format

#### 6.3 Byte stuffing

The technique of byte-stuffing is achieved by trapping reserved bytes in illegal fields, and transforming them into legal byte pairs. Byte values 0xFD, 0xFE, and 0xFF are transformed into a pair of bytes as shown in the table.

| Byte | Transformed into |  |  |

|------|------------------|--|--|

| 0xFD | 0xFD 0x00        |  |  |

| 0xFE | 0xFD 0x01        |  |  |

| 0xFF | 0xFD 0x02        |  |  |

Thus, the bytes reserved for start and stop conditions (0xFE and 0xFF) will never occur within the block.

#### 6.4 Application example (setting PI to 30FF and reading it back for verify)

| To set the PI:         | FE 00 30 FD 02 FF | $\rightarrow$ |

|------------------------|-------------------|---------------|

| To read the PI:        | FE D0 00 02 FF    | $\rightarrow$ |

| The response received: | FE 00 30 FD 02 FF | ←             |

#### 6.5 Firmware update

To allow firmware update, the final equipment must provide the RS232 interface and must allow to be set to one of the modes 0, 1 or 2. The firmware update is realised using a specialized Windows application. Currently (2016) no firmware update has been released yet.

# 7 COMMENTED MEMORY MAP

| Address Parameter Description |     | Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HEX                           | DEC | Parameter   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 00-01                         | 0-1 | PI          | Program Identification code.<br>Identification code of the radio station. Always contains four hexadecimal digits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 02-09                         | 2-9 | PS Buffer   | Program Service name (buffered).<br>Static name of radio station that is displayed on receiver. Max. 8 characters<br>long, redundant characters must be filled as spaces (32).<br>Writing to this region is synchronized with the group order in order to provide<br>the best visual result on most receivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OA                            | 10  | ΡΤΥ         | Program Type (0-31).<br>An identification number to be transmitted with each program item, intended to<br>specify the current Program Type within 32 possibilities.<br>Program type codes (Europe / US):<br>0 – (none) / (none)<br>1 – News / News<br>2 – Affairs / Information<br>3 – Info / Sports<br>4 – Sport / Talk<br>5 – Education / Rock<br>6 – Drama / Classic Rock<br>7 – Cultures / Adult Hits<br>8 – Science / Soft Rock<br>9 – Varied Speech / Top 40<br>10 – Pop Music / Country<br>11 – Rock Music / Oldies<br>12 – Easy Music / Oldies<br>13 – Light Classics Music / Nostalgia<br>14 – Serious Classics / Jazz<br>15 – Other Music / Classical<br>16 – Weather / Rhythm and Blues<br>17 – Finance / Soft Rhythm and Blues<br>18 – Children / Foreign Language<br>19 – Social Affairs / Religious Music<br>20 – Religion / Religious Talk<br>21 – Phone In / Personality<br>22 – Travel / Public<br>23 – Leisure / College<br>24 – Jazz Music / (unassigned)<br>25 – Country Music / (unassigned)<br>26 – National Music / (unassigned)<br>27 – Oldies Music / (unassigned)<br>28 – Folk Music / (unassigned)<br>29 – Documentary / Weather<br>30 – Alarm Test / Emergency Test<br>31 – Alarm / Emergency |

| 0B                            | 11  | DI          | Decoder Identification (0-15).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0C                            | 12  | MS          | Music/Speech switch (0/1).<br>0 – Speech program<br>1 – Music program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0D                            | 13  | ТР          | Traffic Program (0/1).<br>This is a flag to indicate that the tuned program carries traffic announcements.<br>The TP flag must only be set on programs that dynamically switch on the TA<br>identification during traffic announcements. The signal shall be taken into<br>account during automatic search tuning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OE    | 14      | ТА          | Traffic Announcement (0/1).<br>Indicates instantaneous presence (1) of traffic information during<br>broadcasting.<br>When this value is set to 1 by external TA switch, the value specified by TA<br>command has no effect.<br>When this value is set to 1 by TA command, the value set by external TA<br>switch has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-------|---------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0F    | 15      | AFNUM       | Number of Alternative Frequencies (0-15).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 10-1E | 16-30   | AF          | List of Alternative Frequency channels in hexadecimal range of 01-CC (87.6-107.9 MHz). Up to 15 items allowed. Starts at the first address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 1F    | 31      | RTEN        | Bit 0:<br>Enables (1) or disables (0) the Radiotext.<br>Bit 1:<br>Controls the RT A/B type flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 20-5F | 32-95   | RT          | Radiotext.<br>Up to 64 characters long text message to be displayed on receiver in<br>Radiotext format. Redundant characters must be filled as spaces (32).<br>Car radios usually don't support this service, Dynamic PS can be used<br>instead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 60    | 96      | UDG1EN      | Enables (1) or disables (0) the UDG1 transmission. By default (if RT is enabled), the group order on the device output is 0A 0A 0A 0A 2A (UDG1) 0A 0A 0A 0A 2A (UDG1) etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 61-66 | 97-102  | UDG1 Buffer | User Defined Group 1 (buffered)<br>Specifies one free content group in BBBBCCCCDDDD format, which is<br>repeatedly transmitted by the RDS encoder. BBBB, CCCC and DDDD<br>represent the contents of the block B, block C and block D.<br>The RDS encoder calculates the CRC automatically.<br>According to the RDS standard, the block A has not been specified as it is<br>always the PI code.<br>According to the RDS standard, the block C is internally substituted by the PI<br>code whenever block B bit 11 is set to 1, indicating group version <i>B</i> .<br>The PTY and TP services set in the UDG1 group (block B bits 10:5) are<br>ignored and are substituted according to the internal configuration of these<br>services in the RDS encoder.                                                                                                                                    |  |  |  |

| 67-6C | 103-108 | UDG2 Buffer | User Defined Group 2 (buffered)<br>Orders the RDS encoder to send directly RDS group whose content is free.<br>The Group content is in BBBBCCCCDDDD format where BBBB, CCCC and<br>DDDD represent the contents of the block B, block C and block D.<br>The RDS encoder calculates the CRC automatically.<br>According to the RDS standard, the block A has not been specified as it is<br>always the PI code.<br>According to the RDS standard, the block C is internally substituted by the PI<br>code whenever block B bit 11 is set to 1, indicating group version <i>B</i> .<br>The PTY and TP services set in the UDG2 group (block B bits 10:5) are<br>ignored and are substituted according to the internal configuration of these<br>services in the RDS encoder.<br>Using this command, the RDS transmission can then be partially or fully<br>controlled by an external application. |  |  |  |

|    |     |         | ۰<br>۱                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6D | 109 | UDG2CNT | Can be set to 0-8. When set to a value greater than zero, the UDG2 group<br>starts to be inserted from the buffer to the RDS stream. Each transmission will<br>decrease the UDG2CNT byte by 1. When the value counts down to zero, the<br>UDG2 transmission will stop in the next cycle. The buffer content will retain.<br>UDG2 Buffer<br>Copy to transmission buffer<br>87.6 ms<br>Previous RDS group<br>UDG2 RDS group<br>UDG2 RDS group<br>UDG2 RDS group<br>UDG2 RDS group<br>Figure 7.1 – Inserting one UDG2 RDS group<br>When the UDG2CNT is decrementing, the UDG2 groups make a continuous<br>block on the output. Changing the buffer content while the UDG2CNT is<br>greater than zero is not allowed.<br>If high UDG rate is required, the user may read the UDG2CNT byte and test it<br>for zero value in order to recognize that another group can be written to the<br>UDG2 buffer. This allows for fully synchronous UDG transmission. |

| 6E | 110 | EXTSYNC | External pilot synchronisation.<br>1 – Automatic external synchronisation if pilot tone present (default)<br>0 – Forced internal clock source (for mono transmission only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6F | 111 | PHASE   | RDS Signal phase (0-18).<br>Fixes the relative phase shift between the pilot tone and the RDS signal. Has<br>effect only if bit 0 of the EXTSYNC is set to 1 and pilot tone is present.<br>Changing the value by one results in 9.5 degrees phase shift change.<br>The value serves only as a scale, it may not provide real phase shift value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 70 | 112 | STATUS  | Status register – <b>read only</b> .<br>Bit 0:<br>1 – Pilot tone present<br>0 – Pilot tone not present or internal clock source set<br>Bit 1:<br>State of TA that is on air.<br>Bit 2:<br>Indicates if Dynamic PS text loop is running (1) or static PS is displayed (0).<br>Bit 3:<br>Indicates whether the new PS is still waiting in the PS buffer (1) or the PS<br>buffer content has been already copied (0).<br>Bit 7:<br>Indicates whether the RDS subcarrier is on (1) or off (0).                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 71 | 113 | CONTROL | <ul> <li>Control register – write only.</li> <li>Depending on the value written the operation is performed.</li> <li>69 (0x45, 'E'):</li> <li>Stores all RAM content to internal EEPROM. The content will be restored on next power-up.</li> <li>82 (0x52, 'R'):</li> <li>Provokes a hardware reset of the RDS encoder and is equivalent to an "off-on" cycle of the RDS encoder. Must be the only byte written in the START-STOP session.</li> <li>48 (0x30, '0'):</li> <li>Switches off the RDS subcarrier. Must be the only byte written in the START-STOP session.</li> <li>49 (0x31, '1'):</li> <li>Switches on the RDS subcarrier.</li> </ul>                                                                                                                                                                                                                                                                                                    |

| 72 | 114 | SPSPER  | Static PS period (0-255).<br>Specifies the time between two repeats of the Dynamic PS text. Static PS<br>(PS) is displayed during this time. Increasing the value by 1 increases the<br>period by approx. 2.7 seconds.<br>If value 255 is set, the Dynamic PS will be displayed only once, if the<br>DPSNUM address is written.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# **MRDS1322**

| 73    | 115     | DPSMOD  | Display mode for the Dynamic PS text (0-3).<br>0 – Scrolling by fixed 8 characters<br>1 – Scrolling by 1 character<br>2 – Word alignment scrolling<br>3 – Scrolling by 1 character, text separated by spaces at begin and end<br>The dynamic PS text must be longer than 7 characters for mode <b>1</b> .                                                                                                               |

|-------|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74    | 116     | LABPER  | Label period in range of 0-255 used in Dynamic PS mode 0 and 2. Increasing the value by 1 increases the period by approx. 0.54 seconds.                                                                                                                                                                                                                                                                                 |

| 75    | 117     | SCRLSPD | Scrolling PS speed (0/1).<br>Sets high (0) or low (1) speed of scrolling PS transmission (mode 1 and 3).<br>Although setting high speed gives the result looking better, remember that on<br>some receivers or under bad reception conditions the text may be unreadable.<br>The reason has nothing to do with the device and comes out from the fact that<br>scrolling PS has never been included in the RDS standard. |

| 76    | 118     | DPSNUM  | Number of characters in Dynamic PS (0-80). When written, the Dynamic PS text loop restarts.                                                                                                                                                                                                                                                                                                                             |

| 77-C6 | 119-198 | DPS     | Dynamic PS.<br>Up to 80 characters long text message to be displayed on receiver instead of<br>static PS name. Can be used for song titles streaming etc.<br>Before writing new text, set the DPSNUM to 0. After the text is written, set the<br>DPSNUM to corresponding value.                                                                                                                                         |

| C7    | 199     |         | (reserved)                                                                                                                                                                                                                                                                                                                                                                                                              |

| C8-CF | 200-207 | PS      | Program Service name (not buffered).                                                                                                                                                                                                                                                                                                                                                                                    |

#### Notes:

- Buffered address range Content of this address range is not directly used for the RDS transmission. If at

least one byte from the address range is written, after STOP condition on the bus the content is copied to

internal not buffered address range and synchronised with RDS groups order. This prevents transmission of

partial content and mixing old and new strings when the address range is written. For the PS both buffered

and not buffered address ranges are provided.

- Bit order:

| MSB   |       |       |       |       |       |       | LSB   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

Dynamic PS examples for each DPSMOD value:

| Mode 0            | Mode 1   | Mode 2  | Mode 3 |

|-------------------|----------|---------|--------|

| THIS IS           | EXAMPLE  | THIS IS | м      |

| AN EXAMP          | XAMPLE O | AN      | MO     |

| LE OF MO          | AMPLE OF | EXAMPLE | MOD    |

| DE 0              | MPLE OF  | OF MODE | MODE   |

|                   | PLE OF M | 2       | MODE   |

| Ť                 | LE OF MO |         | MODE 3 |

| Ť                 | E OF MOD |         | MODE 3 |

| Ť                 | OF MODE  |         | MODE 3 |

| Ť                 | OF MODE  |         | ODE 3  |

| Ť                 | F MODE 1 |         | DE 3   |

| Ť                 | Е З      |         |        |

| T Label period or | 3        |         |        |

| <b>T</b>          | 3        |         |        |

| ±                 |          |         |        |

- ♥ <sub>Time</sub>

- UDG1 and UDG2 byte order in the block: Higher byte is sent first.

- Application note for general purpose data transmission using UDG groups: It is possible to use last 4 bytes (block C and D) for general purpose data transfers. Longer data may split into 4 bytes segments, sent in sequence. The sequence counter can be put into block B bits 4:0. The group type (block B bits 15:11) should be set to 01100.

## 8 TEST CIRCUIT

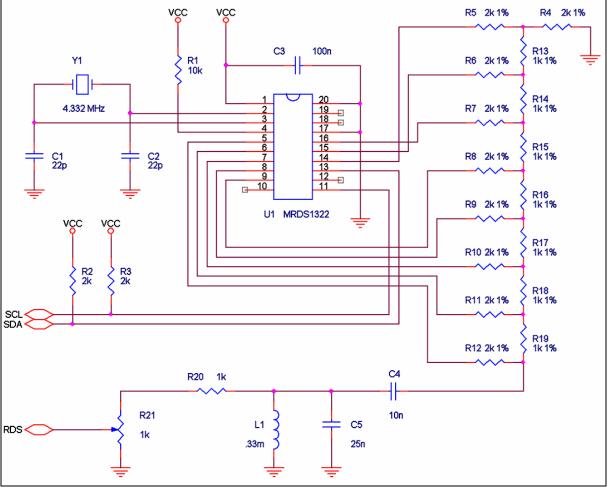

# 8.1 Schematic diagram

Figure 8.1 – Test circuit schematic diagram.

# 8.2 Characteristics

The test circuit is characterized as follows:

- Power supply voltage: 5 V

- Communication bus: I<sup>2</sup>C

- DAC type: R/2R 8-bit

- Output filter: simple LC element resonating at 57 kHz (L1 serial resistance 1.9 Ω; C5 is a plastic film type, a value of 25 nF has been chosen to compensate the L1 inductance loss at higher frequencies)

- Output level: adjustable 0 to 1 V pp

- LED output, TA input: not used

- Pilot input: not used (switched to internal reference)

# 8.3 Output analysis

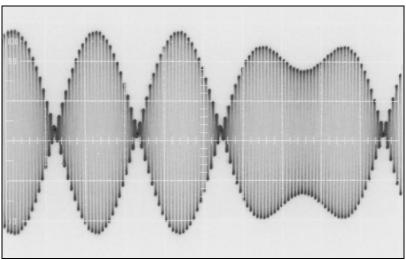

Figure 8.2 – Output RDS signal on oscilloscope (horizontal: 200 µs/div, vertical: 200 mV/div).

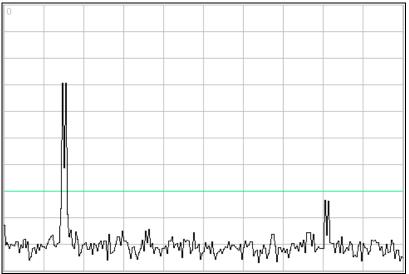

**Figure 8.3** – Output spectrum measured on transmitter input (horizontal: 37.5 kHz/div, vertical: -10 dB/div; 0 dB corresponds to 75 kHz peak FM deviation; peak deviation caused by RDS: 3.4 kHz).

Figure 8.4, 8.5 – Output LC filter characteristics.

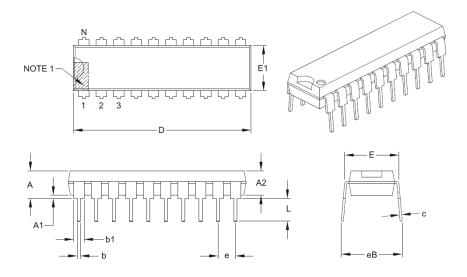

# 9 PACKAGE DETAILS

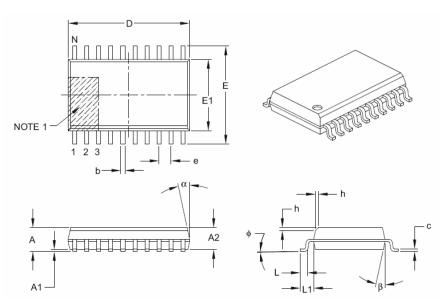

| ↑ 20-Lead PDIP – 300 mil Body |      |          |       |  |  |  |

|-------------------------------|------|----------|-------|--|--|--|

| Symbol                        | MIN  | NOM      | MAX   |  |  |  |

| Ν                             |      | 20       |       |  |  |  |

| е                             |      | .100 BSC |       |  |  |  |

| А                             | -    | -        | .210  |  |  |  |

| A2                            | .115 | .130     | .195  |  |  |  |

| A1                            | .015 | -        | -     |  |  |  |

| E                             | .300 | .310     | .325  |  |  |  |

| E1                            | .240 | .250     | .280  |  |  |  |

| D                             | .980 | 1.030    | 1.060 |  |  |  |

| L                             | .115 | .130     | .150  |  |  |  |

| С                             | .008 | .010     | .015  |  |  |  |

| b1                            | .045 | .060     | .070  |  |  |  |

| b                             | .014 | .018     | .022  |  |  |  |

| eB                            | -    | -        | .430  |  |  |  |

| Symbol | MIN       | NOM      | MAX  |  |  |

|--------|-----------|----------|------|--|--|

| Ν      |           | 20       |      |  |  |

| е      |           | 1.27 BSC |      |  |  |

| Α      | -         | -        | 2.65 |  |  |

| A2     | 2.05      | -        | -    |  |  |

| A1     | 0.10      | -        | 0.30 |  |  |

| E      | 10.30 BSC |          |      |  |  |

| E1     | 7.5 BSC   |          |      |  |  |

| D      | 1         | 2.80 BSC | )    |  |  |

| h      | .25       | -        | 0.75 |  |  |

| L      | .40       | -        | 1.27 |  |  |

| L1     |           | 1.40 REF |      |  |  |

| Φ      | 0°        | -        | 8°   |  |  |

| С      | 0.20      | -        | 0.33 |  |  |

| b      | 0.31      | -        | 0.51 |  |  |

| α      | 5°        | -        | 15°  |  |  |

| β      | 5°        | -        | 15°  |  |  |

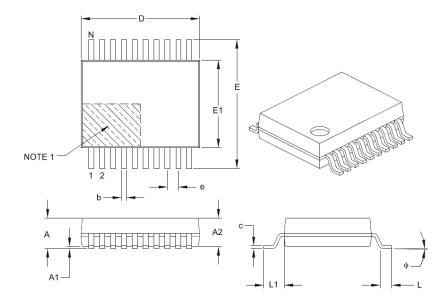

| ↑ 20-Lead SSOP – 5.30 mm Body |          |          |      |  |  |  |

|-------------------------------|----------|----------|------|--|--|--|

| Symbol                        | MIN      | NOM      | MAX  |  |  |  |

| Ν                             |          | 20       |      |  |  |  |

| е                             |          | 0.65 BSC |      |  |  |  |

| Α                             | -        | -        | 2.00 |  |  |  |

| A2                            | 1.65     | 1.75     | 1.85 |  |  |  |

| A1                            | 0.05     | -        | -    |  |  |  |

| E                             | 7.40     | 7.80     | 8.20 |  |  |  |

| E1                            | 5.00     | 5.30     | 5.60 |  |  |  |

| D                             | 6.90     | 7.20     | 7.50 |  |  |  |

| L                             | .55      | 0.75     | 0.95 |  |  |  |

| L1                            | 1.25 REF |          |      |  |  |  |

| Φ                             | 0°       | 4°       | 8°   |  |  |  |

| С                             | 0.09     | -        | 0.25 |  |  |  |

| b                             | 0.22     | -        | 0.38 |  |  |  |

Note 1: Pin 1 visual index feature may vary, but must be located within the hatched area.