## **Change Summary**

#### **CHANGES**

| No. | Applicable Section              | Description Page(s)                                                                                                                                                                                                 |

|-----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | Application Circuit Figs. 2 & 3 | Add reference note. 3, 4                                                                                                                                                                                            |

| 2.  | Functional Specifications       | Correct a) 'Operating Frequency on DRV1 & 2 Pin' Min. Typ. and Max. limits, b) 'LPWM Frequency' Min. and Typ. limits, c) 'Ignition Time' parameter title, and d) 'Lamp Current Reference' parameter title and unit. |

| 3.  | Functional Description, 4.      | Last sentence, add "CT" pin number.                                                                                                                                                                                 |

| 4.  | Functional Description, 5.      | Last sentence, add "pin 2" name, and correct formula.                                                                                                                                                               |

| 5.  | Functional Description, 8.      | 4 <sup>th</sup> line, correct to read "voltage at the CCFL for approximately two seconds."                                                                                                                          |

| 6.  | Functional Description, 9.      | 3 <sup>rd</sup> paragraph, 5 <sup>th</sup> line, correct to read "is set by external capacitors C9 and C11 connected to C7 (Pin 7, 8 2)", deleting " CT (Pin 2)" from the following sentence.                       |

| 7.  | Functional Description, 9.      | 4 <sup>th</sup> paregraph, correct formula and add last sentence.                                                                                                                                                   |

| 8.  | Throughout data sheet           | Miscellaneous corrections                                                                                                                                                                                           |

## **REVISION HISTORY**

|              | 3000000       | /80/10 39 | 20000       | 7000 4000 | 2007 |          | MOCO, 10 10  |

|--------------|---------------|-----------|-------------|-----------|------|----------|--------------|

| Revision No. |               |           | Description | of change |      | <b>N</b> | Release Date |

| 0.90         | Initial relea | SA        | 4           |           |      |          | 03/27/08     |

#### **DEVIN LAI**

## OZ9RR

## **LCD Monitor CCFL Inverter Controller**

#### **FEATURES**

- Low cost LCD monitor inverter solution

- Constant operating frequency

- Operating frequency can be synchronized with external signal

- Integrated synchronized PWM dimming control with wide dimming range

- Built-in intelligence for ignition and normal operation of CCFLs

- Built-in open-lamp protection and overvoltage protection

- Optimized soft-start function

- Higher reliability and longer life

- Supports multiple CCFLs

- Minimum external components

## ORDERING INFORMATION

OZ9RRG - 8 pin plastic SOIC OZ9RRD - 8 pin plastic DIP

### GENERAL DESCRIPTION

The patent pending OZ9RR is a cost-effective CCFL (Cold Cathode Fluorescent Lamp) Power Management controller designed for multiple CCFL LCDM (Liquid Crystal Display Monitor) applications.

OZ9RR operates at a constant operating frequency. The operating frequency can be synchronized with an external signal that eliminates any undesired interference between the controller and LCD panel.

The controller provides a wide dimming range control with a low-frequency Pulse Width Modulation (LPWM) dimming function. The control logic provides a regulated ignition voltage and appropriate protection for over-voltage or over-current conditions.

The OZ9RR offers a high level of integration, while maintaining flexibility and high-efficiency operation that reduces component heating. This results in higher reliability and longer CCFL life. The proprietary (patent pending) design technique provides a simpler, lower-cost system solution.

Operating in a zero-voltage switching, push-pull topology, the OZ9RR achieves high power conversion efficiency. The highly integrated controller encompasses current and voltage regulation, soft-start operation, over-voltage protection and an external enabling function while maintaining a high-degree of design flexibility. The application requires a minimum number of off-the-shelf components.

The CCFL backlight controller is designed for a wide range of input voltages. It provides a wide dimming range by converting an external analog control input into a built-in LPWM dimming function. The controller converts unregulated DC voltages into a nearly sinusoidal lamp voltage and current waveforms.

The OZ9RR is available in 8-pin SQIC and 8-pin PDIP packages.

OZ9RR is specified over the commercial temperature range from 0°C to 70°C.

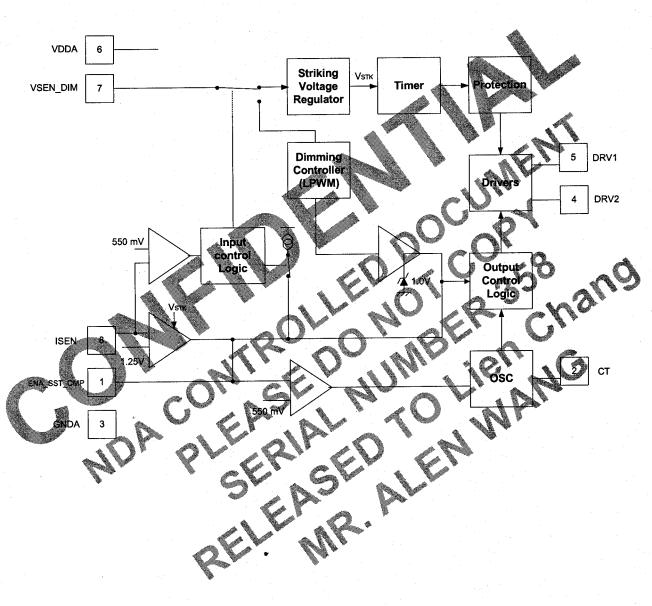

Figure 1. OZ9RR Functional Block Diagram

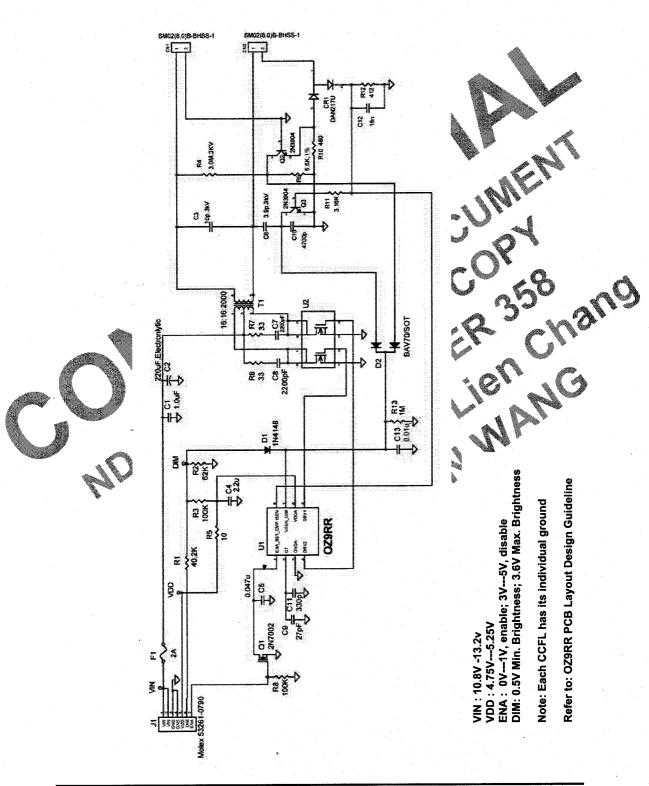

Figure 2. OZ9RR Typical Application Circuit: Separate Ground

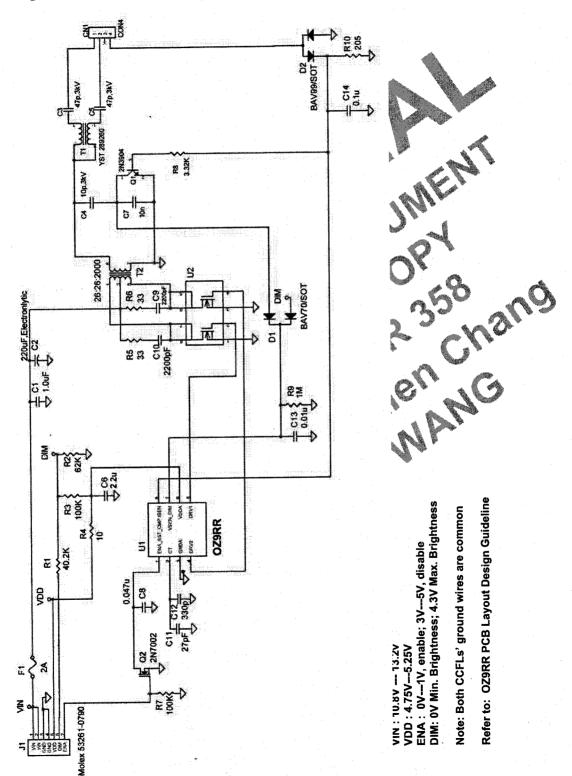

Figure 3. OZ9RR Typical Application Circuit: Common Ground

#### **OZ9RR PIN DESCRIPTION**

| Names       | Pin No. | I/O | Description                                                         |

|-------------|---------|-----|---------------------------------------------------------------------|

| ENA SST CMP | 1       | 1/0 | Enable, Soft Start Time and Compensation of Current Error Amplifier |

| СТ          | 2       | 1/0 | Timing Capacitor to Set Operating Frequency                         |

| GNDA        | 3       |     | Ground                                                              |

| DRV2        | 4       | 0   | N MOSFET Drive Output                                               |

| DRV1        | 5       | 0   | N MOSFET Drive Output                                               |

| VDDA        | 6       |     | Supply Voltage Input                                                |

| VSEN DIM    | 7       | 1   | Voltage Sense_Input Analog Signal for PWM Dimming Control           |

| ISEN        | 8       | ı   | Lamp Current Detection & Control                                    |

# ABSOLUTE MAXIMUM RATINGS WITH RESPECT TO INPUT POWER SOURCE RETURN REFERENCE

| Input Voltage VDDA | 7.0V <sup>(1)</sup> |

|--------------------|---------------------|

| GNDA               | +/- 0.3V            |

| Logic inputs       | -0.3V to VDDA +0.3V |

| Operating temp.       |     | 0°C    | to +70 | °C |

|-----------------------|-----|--------|--------|----|

| Operating junction te | mp. |        | 125    | °C |

| Storage temp.         |     | -55 °C | to 150 | °C |

## RECOMMENDED OPERATING RANGE

|   | Input Voltage   | 4.5V to 5.5V    |

|---|-----------------|-----------------|

| - | f <sub>op</sub> | 30KHz to 150KHz |

Note <sup>(1)</sup>: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The "Functional Specifications" table will define the conditions for actual device operation. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

## **FUNCTIONAL SPECIFICATION**

| Parameter                                 | Symbol           | Test Conditions                                                            |            | Limits |      | Unit |

|-------------------------------------------|------------------|----------------------------------------------------------------------------|------------|--------|------|------|

|                                           |                  | VDDA=5V; CT=357pF;<br>CssT=12.1nF; Tamb=25°C<br>unless otherwise specified | Min        | Тур    | Max  |      |

| Supply Current                            |                  |                                                                            |            |        |      |      |

| Stand By                                  | I <sub>dds</sub> | V1=0V; V8=0V                                                               | -          | 350    | 470  | μΑ   |

| Operating                                 | l <sub>dd</sub>  | V1=2V; V8=0V                                                               | -          | 3.9    | 6.0  | mA   |

| Soft Start Current Source                 | ISST             | V1=0V; V8=0V; V7=0V                                                        | 2.4        | 3.0    | 3.5  | μΑ   |

| Under Voltage Lockout                     | UVLO             | V1=1V; VDDA from 0V to 5V                                                  | 3.2        | 3.8    | 4.2  | V    |

| ENA_SST_CMP Pin - Low                     | VCMP             |                                                                            | 0.96       | 1.07   | 1.10 | V    |

| CT Pin Peak Valley                        |                  |                                                                            |            |        |      |      |

| CT Pin Peak                               | Vpeak            | V1=2V; V8=660mV; V7=2.8V                                                   | 2.90       | 3.06   | 3.20 | V    |

| CT Pin Valley                             | Vvalley          | V1=2V; V8=660mV; V7=2.8V                                                   | 0.95       | 1.02   | 1.15 | V    |

| Operating Frequency on<br>DRV1 & DRV2 Pin | fop              | V1=1.2V; V8=660mV;<br>V7=2.8V                                              | 44.0       | 48.5   | 53.0 | kHz  |

| LPWM Frequency                            | fLF              | V <sub>1</sub> =1.2V; V <sub>8</sub> =660mV;<br>V <sub>7</sub> =1.5V       | 190        | 210    | 231  | Hz   |

| Dimming                                   |                  |                                                                            | English (F |        |      |      |

| Minimum Brightness                        | VSEN_DIM         | Typical 10%                                                                | 7-43       | -      | 0.22 | V    |

| Maximum Brightness                        | VSEN_DIM         |                                                                            | 2.39       | X 0    |      | · V  |

| Pulse Width on DRV1 & DRV2 (active high)  |                  |                                                                            |            |        |      |      |

| Minimum                                   |                  | V1=0.8V; V8=0V; V7=0V                                                      | 0.1        | 0.2    | 0.3  | μsec |

| Maximum                                   |                  | V1=3V; V8=0V; V7=0V                                                        | 6.6        | 6.8    | 7.0  | µsec |

| Over Voltage Protection<br>Threshold      | OVP (V7)         | V1=1.5V; V8=0V                                                             | 2.90       | 3.10   | 3.25 | ٧    |

| Open Lamp Protection<br>Threshold         | OPLAMP<br>(V1)   | Va=0V; V7=0V                                                               | 3.4        | 3.8    | 4.2  | V    |

| Ignition Time<br>( Open Lamp Time Out )   | 111124           | V8=0V; V7=0V                                                               | 1.7        | 2.0    | 2.3  | sec  |

| Lamp Current Reference<br>Voltage         | ISEN             | 100 B                                                                      | 1,19       | 1.25   | 1.31 | V    |

| V1 (ENA_SST_CMP Pin)<br>Threshold         |                  |                                                                            | 500        | 550    | 600  | mV   |

| Drivers                                   |                  |                                                                            |            |        |      |      |

| DRV1                                      | Ron              | For lout= 70 mA                                                            | 10         | 18     | 26   | Ω    |

| DRV2                                      | Ron              | For lout= 70 mA                                                            | 10         | 18     | 26   | Ω    |

Note: Parameters, symbol and test conditions columns, Vx=VPIN NUMBER

#### **FUNCTIONAL DESCRIPTION**

#### 1. Power Conversion

The power train uses a zero voltage switching push-pull topology to provide symmetrical drive pulses to the tank circuit that includes the transformer(s), output capacitors and the CCFL/panel load, to yield quasi-sinusoidal CCFL voltage and current waveforms. High-efficiency operation of the OZ9RR yields lower heat dissipation for the inverter system resulting in higher reliability.

OZ9RR controller provides a low system cost.

Refer to Figures 1 and 2 on pages 2 and 3, respectively for the following sections.

#### 2. Enable

The OZ9RR is enabled when the voltage on Pin 1 is greater than 0.55V.

#### 3. Soft Start (SST)

Connecting an external capacitor to Pin 1 provides the SST function. A charging current is provided to capacitor C5: At Start-up, as capacitor C5 charges, the voltage level controls the gradual increase in power to the transformer. This reduces in-rush current and provides reliable operation to the CCFL.

## 4. Ignition

The ignition process requires a higher striking frequency to strike the CCFL. The striking frequency is approximately 1.3 times the normal operating frequency. The striking frequency is determined by CT (Pin 2) external capacitors, C9 and C11.

## 5. Normal Operation

Once the CCFL is ignited and current is sensed at Pin 8 (ISEN), the control loop regulates the CCFL current. The operating frequency is determined by the external capacitors C<sub>7</sub>(C9 & C11) at CT (Pin 2), where the approximate operating frequency is calculated by the following equation.

$$f_{op} = \frac{19 \times 10^3}{1.1 \times C_T [pF]}$$

[kHz]

#### 6. Over-Voltage Protection

The control logic protects the transformer from an abnormal high voltage at the secondary output.

During start up, VSEN\_DIM (Pin 7) senses the voltage on the transformer secondary. When VSEN reaches 3V, the output voltage is regulated. An internal timer is activated to provide sufficient time for CCFL ignition. If no current is sensed after approximately 2.0 seconds, the OZ9RR shuts off. Toggling the enable signal from low to high will resume normal operation.

#### 7. Open Lamp Protection

When a CCFL is removed or damaged during normal operation, the QZ9RR shuts off the output drives. When the damaged lamp is replaced, toggling the enable pin from low to high resumes normal operation.

# 8. Aged CCFL Ignition

During the ignition process, the controller senses the voltage at the CCFL. For an open-circuit condition, the power train delivers a regulated voltage at the CCFL for approximately two seconds. This is to ensure that any aged, slow-turn-on CCFL is provided with sufficient voltage and time to ignite.

## 9. Dimming Control

The OZ9RR internal LPWM dimming control circuitry provides a wide low-frequency dimming range. The input to Pin 7 (VSEN\_DIM) is an analog voltage of 0.2V to 2.3V that produces a LPWM duty cycle of 10% to 100%.

The output of the LPWM signal has a duty cycle proportional to the input dimming signal command (VDIM). A resistive network (R1, R2 and R3) is inserted between the external dimming input and Pin 7 to provide user flexibility for different dimming input voltage ranges, such as 0V to 3V or 0V to 5V.

A wide dimming range is achieved by utilizing LPWM control method, via the low-frequency PWM generator circuitry. OZ9RR operates in a constant frequency mode, in which the frequency is set by external capacitors C9 and C11 connected to CT (Pin 2). The operating frequency

# Preliminary OZ9RR

and LPWM frequency are internally synchronized. The operating frequency can also be synchronized to the LCD monitor system by providing an external signal to pin 2. This eliminates any undesired interference between the controller and LCD panel, as the interference is usually associated with variable-frequency design. Interference may result in a poor user experience because of "waterfall" display distortion and other poor display appearance.

The approximate dimming frequency (low frequency) is internally generated and calculated using the following equation:

$$f_F = \frac{75 \times 10^3}{\text{Ct [pF]}}$$

[Hz]

Please contact your local field office for implementation details.

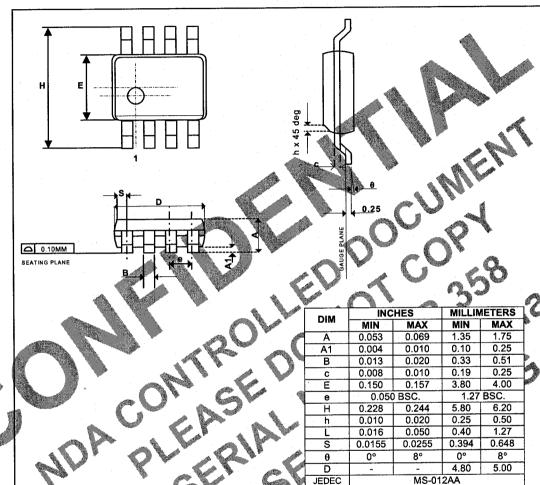

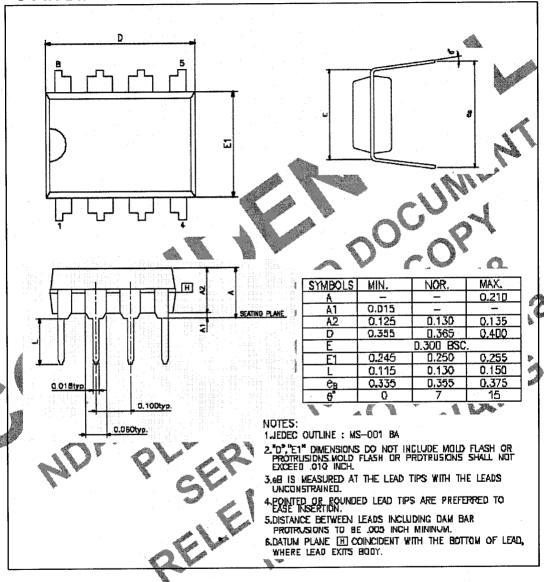

## PACKAGE INFORMATION

#### 8-PIN SOIC

#### Notes:

Controlling dimensions are in millimeter (mm):

Pin #1 count orientation shall be at counterclockwise direction as viewed in live-bug position.

## **PACKAGE INFORMATION**

#### 8-PIN DIP

#### **IMPORTANT NOTICE**

No portion of  $O_2$ Micro specifications/datasheets or any of its subparts may be reproduced in any form, or by any means, without prior written permission from  $O_2$ Micro.

O<sub>2</sub>Micro and its subsidiaries reserve the right to make changes to their datasheets and/or products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

O<sub>2</sub>Micro warrants performance of its products to the specifications applicable at the time of sale in accordance with O<sub>2</sub>Micro's standard warranty. Testing and other quality control techniques are utilized to the extent O<sub>2</sub>Micro deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customer acknowledges that O<sub>2</sub>Micro products are not designed, manufactured or intended for incorporation into any systems or products intended for use in connection with life support or other hazardous activities or environments in which the failure of the O<sub>2</sub>Micro products could lead to death, bodily injury, or property or environmental damage ("High Risk Activities"). O<sub>2</sub>Micro hereby disclaims all warranties, and O<sub>2</sub>Micro will have no liability to Customer or any third party, relating to the use of O<sub>2</sub>Micro products in connection with any High Risk Activities.

Any support, assistance, recommendation or information (collectively, "Support") that Q2Micro may provide to you (including, without limitation, regarding the design, development or debugging of your circuit board or other application) is provided "AS IS." Q2Micro does not make, and hereby disclaims, any warranties regarding any such Support, including, without limitation, any warranties of merchantability or fitness for a particular purpose, and any warranty that such Support will be accurate or error free or that your circuit board or other application will be operational or functional. Q2Micro will have no liability to you under any legal theory in connection with your use of or reliance on such Support.

COPYRIGHT © 2003, O2Micro International Limited