## ST92195C/D

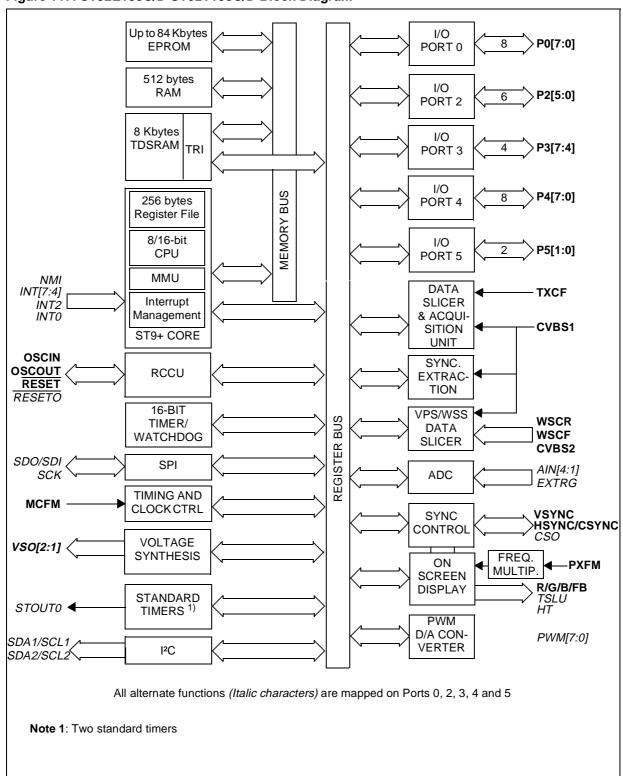

# 48-96 Kbyte ROM HCMOS MCU WITH ON-SCREEN DISPLAY AND TELETEXT DATA SLICER

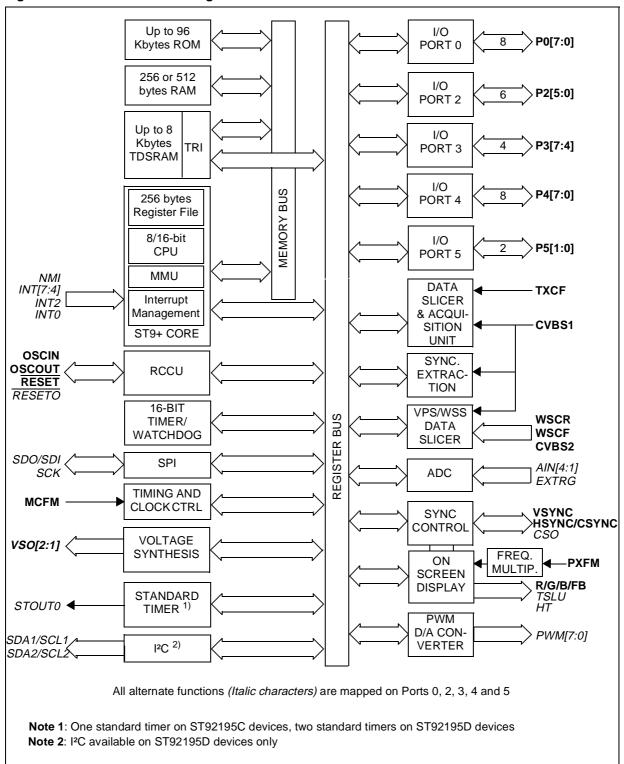

- Register File based 8/16 bit Core Architecture with RUN, WFI, SLOW and HALT modes

- 0°C to +70°C operating temperature range

- Up to 24 MHz. operation @ 5V±10%

- Min. instruction cycle time: 165ns at 24 MHz.

- 48, 56, 64, 84 or 96 Kbytes ROM

- 256 bytes RAM of Register file (accumulators or index registers)

- 256 to 512 bytes of on-chip static RAM

- 2 or 8 Kbytes of TDSRAM (Teletext and Display Storage RAM)

- 28 fully programmable I/O pins

- Serial Peripheral Interface

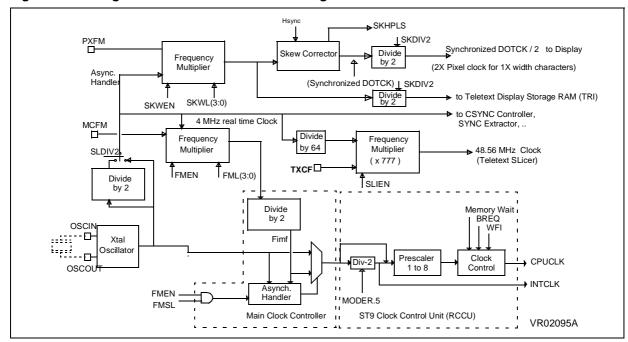

- Flexible Clock controller for OSD, Data Slicer and Core clocks running from a single low frequency external crystal.

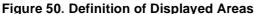

- Enhanced display controller with 26 rows of 40/80 characters

- 2 sets of 512 characters

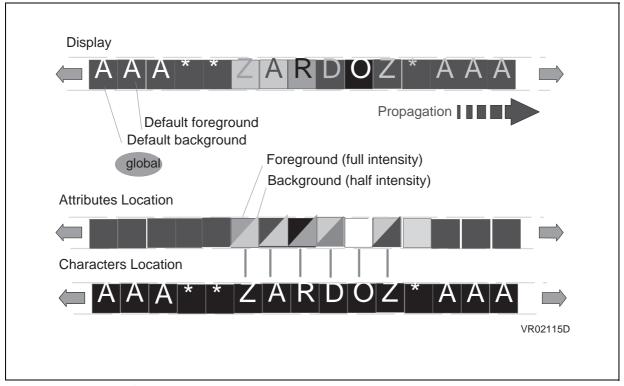

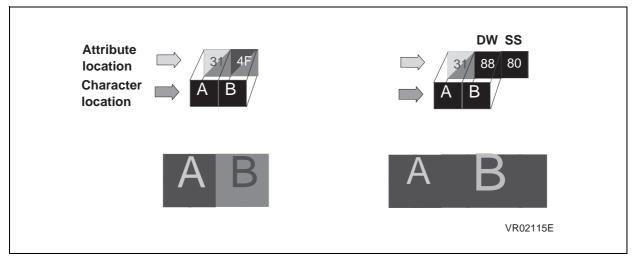

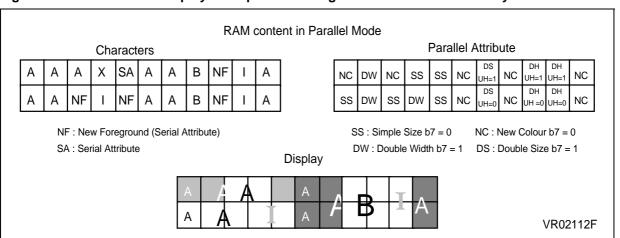

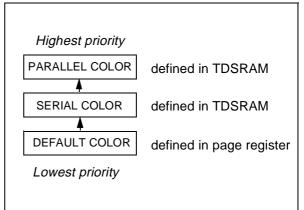

- Serial and Parallel attributes

- 10x10 dot matrix, definable by user

- 4/3 and 16/9 supported in 50/60Hz and 100/ 120 Hz mode

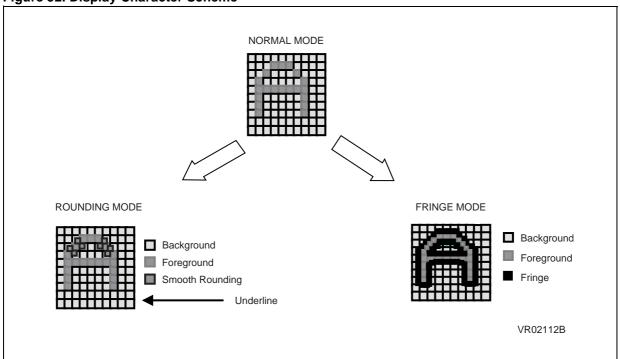

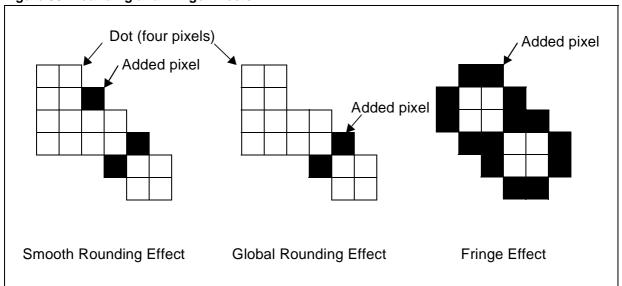

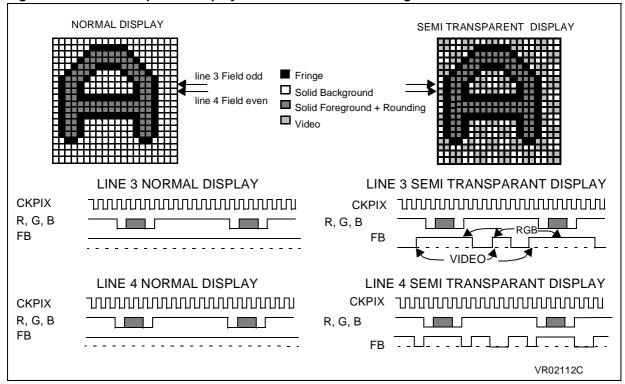

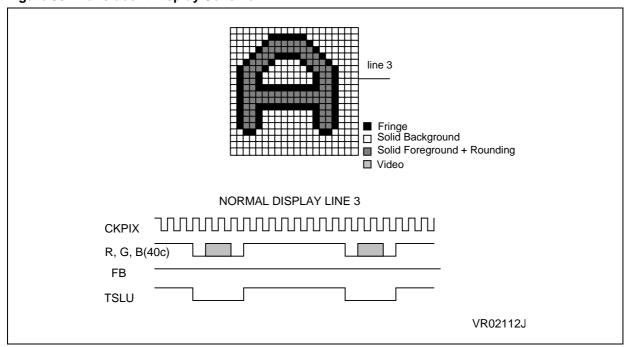

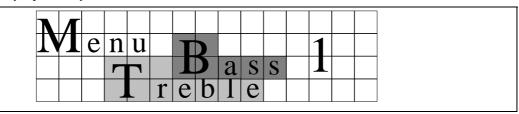

- Rounding, fringe, double width, double height, scrolling, cursor, full background color, halfintensity color, translucency and half-tone modes

- Teletext unit, including Data Slicer, Acquisition Unit and up to 8 Kbytes RAM for data storage

- VPS and Wide Screen Signalling slicer

- Integrated Sync Extractor and Sync Controller

- 14-bit Voltage Synthesis for tuning reference voltage

- Up to 6 external interrupts plus one Non-Maskable Interrupt

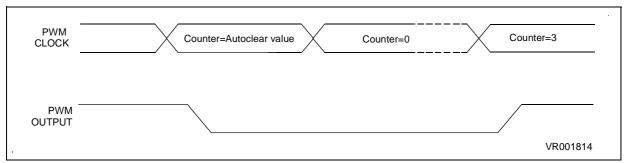

- 8 x 8-bit programmable PWM outputs with 5V open-drain or push-pull capability

- 16-bit watchdog timer with 8-bit prescaler

- 1 or 2 16-bit standard timer(s) with 8-bit prescaler

- I<sup>2</sup>C Master/Slave (on some devices)

- 4-channel A/D converter; 5-bit guaranteed

- Rich instruction set and 14 addressing modes

- Versatile development tools, including Assembler, Linker, C-compiler, Archiver, Source Level Debugger and hardware emulators with Real-Time Operating System available from third parties

- Pin-compatible EPROM and OTP devices available

#### **Device Summary**

| Device    | ROM | RAM | TDSRAM | I <sup>2</sup> C | Timer |  |

|-----------|-----|-----|--------|------------------|-------|--|

| ST92195C3 |     | 256 | 2K     |                  |       |  |

| ST92195C4 | 48K |     | 6K     |                  |       |  |

| ST92195C5 |     |     |        |                  |       |  |

| ST92195C6 | 56K | 512 |        | No               | 1     |  |

| ST92195C7 | 64K | 312 | 8K     |                  |       |  |

| ST92195C8 | 84K |     |        |                  |       |  |

| ST92195C9 | 96K |     |        |                  |       |  |

| ST92195D5 | 48K |     |        |                  |       |  |

| ST92195D6 | 56K | 512 | 8K     | Yes              | 2     |  |

| ST92195D7 | 64K |     |        |                  |       |  |

October 2003 1/249

## Table of Contents —

| <b>ST92</b> | 21950          | C/D                                | 1        |

|-------------|----------------|------------------------------------|----------|

| 1 GEN       | ERAL C         | DESCRIPTION                        | 7        |

| 1.1         | INTRO          | DUCTION                            | 7        |

|             | 1.1.1          | ST9+ Core                          | 7        |

|             | 1.1.2          | Power Saving Modes                 | 7        |

|             | 1.1.3          | I/O Ports                          | 7        |

|             | 1.1.4          | TV Peripherals                     | 7        |

|             | 1.1.5          | On Screen Display                  | 7        |

|             | 1.1.6          | Teletext and Display Storage RAM   |          |

|             | 1.1.7          | Teletext, VPS and WSS Data Slicers |          |

|             | 1.1.8          | gyg                                |          |

|             |                | PWM Output                         |          |

|             |                | Serial Peripheral Interface (SPI)  |          |

|             |                | Standard Timer (STIM)              |          |

|             |                | I <sup>2</sup> C Bus Interface     |          |

| 4.0         |                | Analog/Digital Converter (ADC)     |          |

| 1.2         |                | ESCRIPTION                         |          |

|             |                | I/O Port Alternate Functions.      |          |

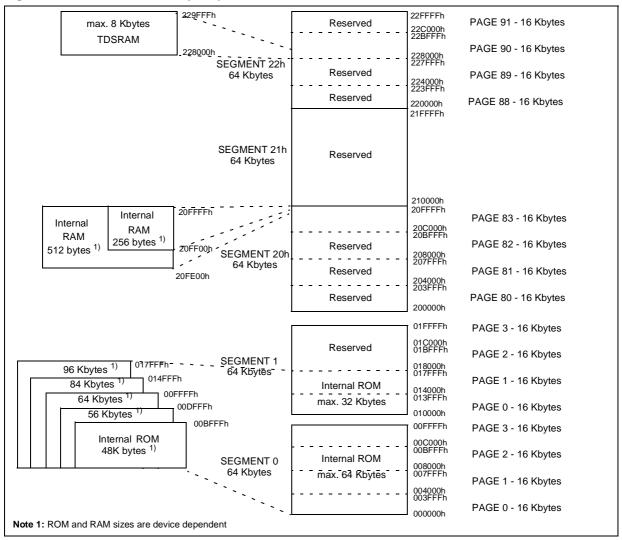

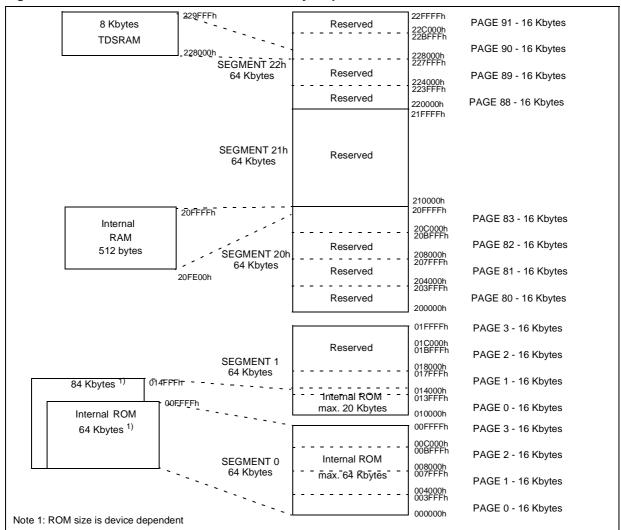

| 1.3         | MEMC           | PRY MAP                            | 17       |

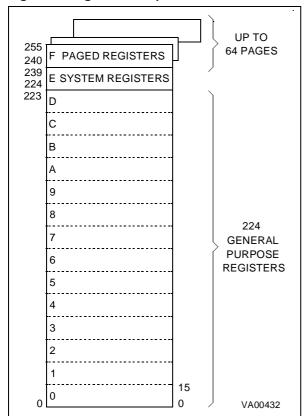

| 1.4         | REGIS          | STER MAP                           | 18       |

| 2 DEVI      | CE AR          | CHITECTURE                         | 24       |

| 2.1         | CORE           | ARCHITECTURE                       | 24       |

| 2.2         | MEMC           | RY SPACES                          | 24       |

|             |                | Register File                      |          |

|             |                |                                    |          |

| 23          |                | EM REGISTERS                       |          |

|             | 2.3.1          | Central Interrupt Control Register |          |

|             | _              | Flag Register                      |          |

|             | 2.3.3          |                                    |          |

|             |                | Paged Registers                    |          |

|             | 2.3.5          |                                    |          |

|             | 2.3.6          | Stack Pointers                     |          |

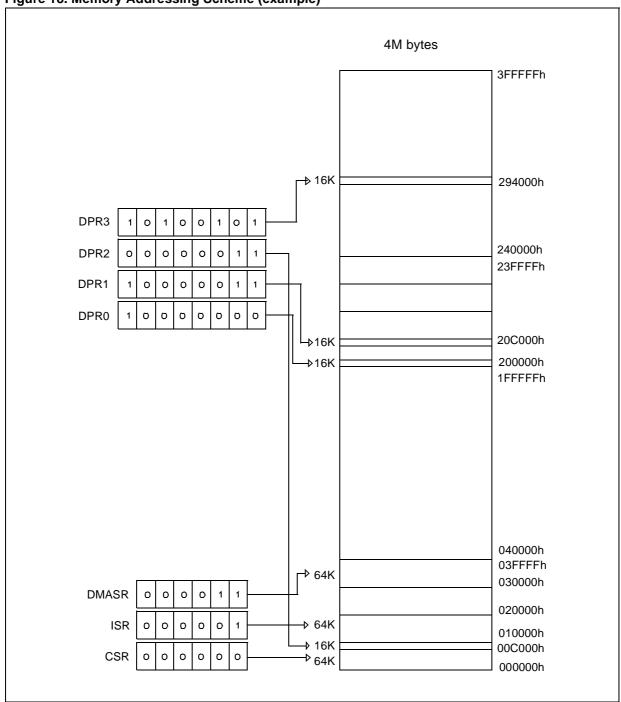

| 2.4         | MEMO           | RY ORGANIZATION                    | 35       |

| 2.5         | MEMO           | RY MANAGEMENT UNIT                 | 36       |

|             |                | ESS SPACE EXTENSION                |          |

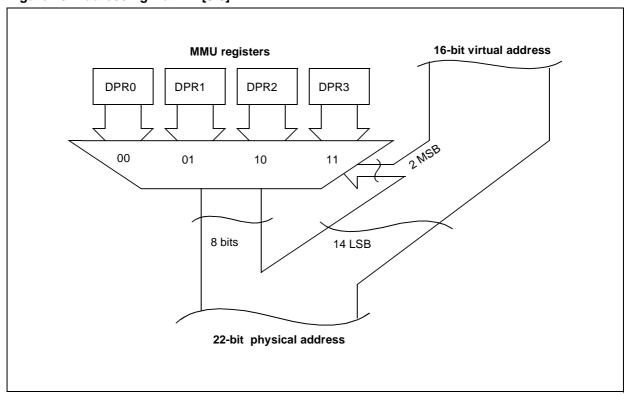

| 2.0         |                | Addressing 16-Kbyte Pages          |          |

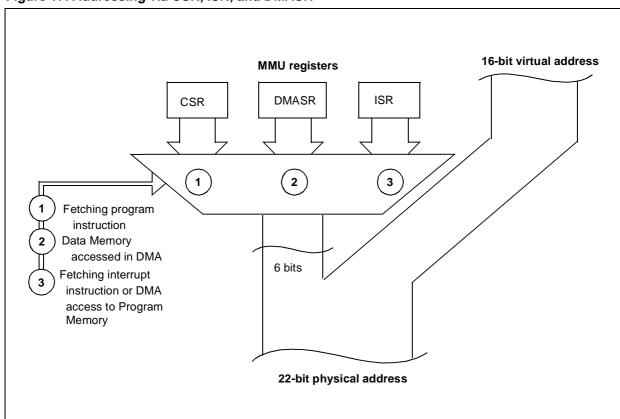

|             |                | Addressing 64-Kbyte Segments       |          |

| 27          |                | REGISTERS                          |          |

| 2.1         |                |                                    |          |

|             | 2.7.1          | DPR[3:0]: Data Page Registers      |          |

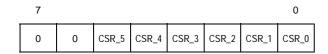

|             | 2.7.2<br>2.7.3 | CSR: Code Segment Register         |          |

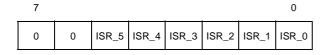

|             | 2.7.3          |                                    |          |

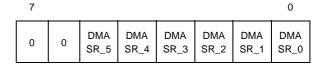

| 2 Q         |                | DMASR: DMA Segment Register        |          |

| 2.0         |                |                                    |          |

|             | 2.8.1          | Normal Program Execution           | 42<br>42 |

|             | / 0 /          | HIIEHUDIS                          | 4/       |

## Table of Contents

|     |     | 2.8.3 | DMA                                         | 42 |

|-----|-----|-------|---------------------------------------------|----|

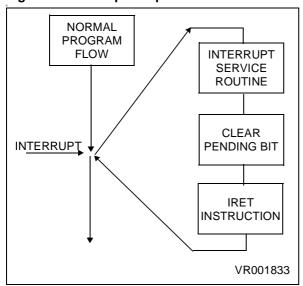

| 3 I | NTE | RRUPT | S                                           | 43 |

|     | 3.1 | INTRO | DUCTION                                     | 43 |

|     | 3.2 | INTER | RUPT VECTORING                              | 43 |

|     |     |       | Divide by Zero trap                         |    |

|     |     | 3.2.2 | Segment Paging During Interrupt Routines    | 44 |

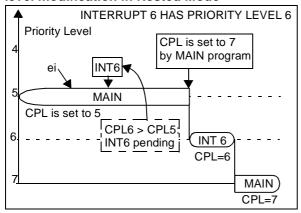

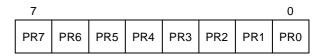

|     |     |       | RUPT PRIORITY LEVELS                        |    |

|     | 3.4 |       | RITY LEVEL ARBITRATION                      |    |

|     |     |       | Priority Level 7 (Lowest)                   |    |

|     |     |       | Maximum Depth of Nesting                    |    |

|     |     |       | Dynamic Priority Level Modification         |    |

|     | 3.5 |       | RATION MODES                                |    |

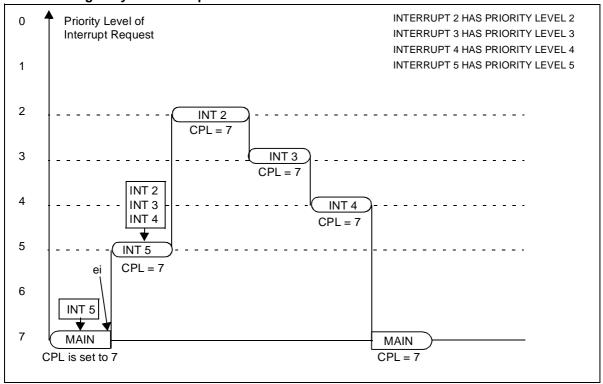

|     |     | 3.5.1 | Concurrent Mode                             | 45 |

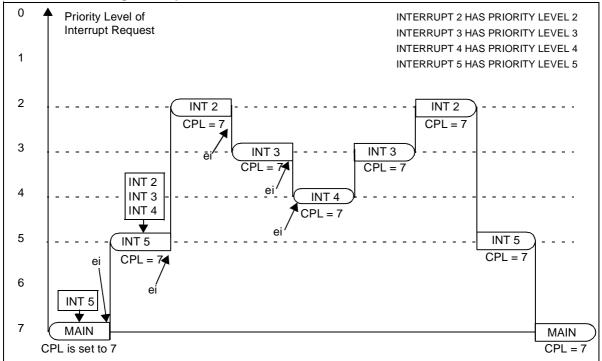

|     |     |       | Nested Mode                                 |    |

|     |     |       | RNAL INTERRUPTS                             |    |

|     |     |       | EVEL INTERRUPT                              |    |

|     |     |       | IIP PERIPHERAL INTERRUPTS                   |    |

|     |     |       | RUPT RESPONSE TIME                          |    |

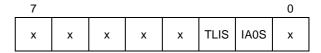

|     |     |       | RUPT REGISTERS                              |    |

| 4 I |     |       | CLOCK CONTROL UNIT (RCCU)                   |    |

|     |     |       | DUCTION                                     |    |

|     |     |       | Γ/STOP MANAGER                              |    |

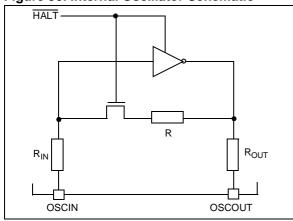

|     |     |       | LATOR CHARACTERISTICS                       |    |

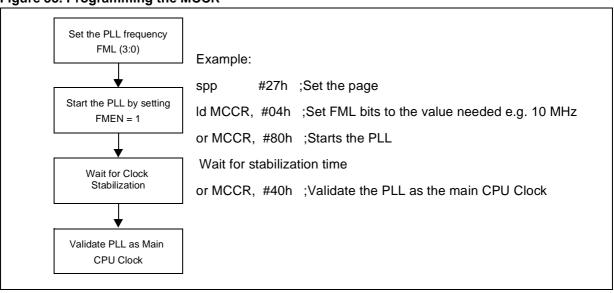

|     |     |       | K CONTROL REGISTERS                         |    |

|     |     |       | CONTROL UNIT REGISTERS                      |    |

| 5   |     |       | CLOCK CONTROLLER                            |    |

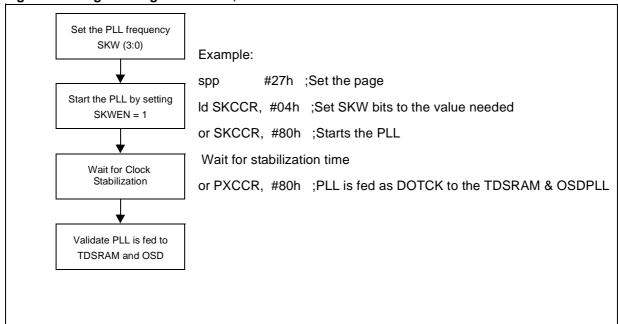

|     |     |       | JENCY MULTIPLIERS                           |    |

|     | 5.2 |       | TER DESCRIPTION                             |    |

|     |     |       | Register Mapping                            |    |

| 6 I |     |       | POLICITION                                  |    |

|     |     |       | DUCTION                                     |    |

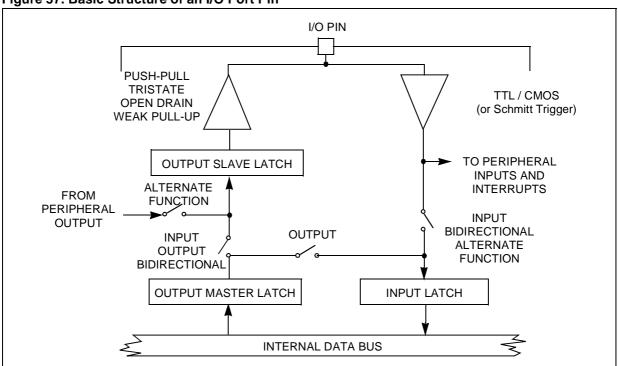

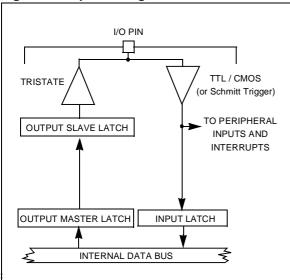

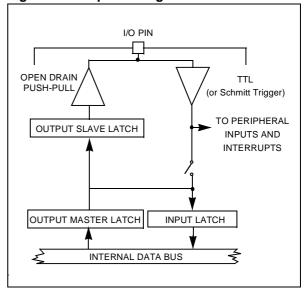

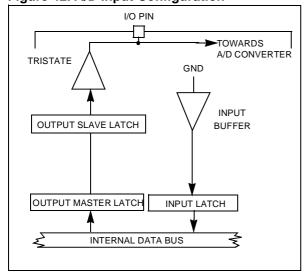

|     |     |       | FIC PORT CONFIGURATIONS                     |    |

|     |     |       | CONTROL REGISTERS                           |    |

|     |     |       | OUTPUT BIT CONFIGURATION                    |    |

|     | 6.5 |       | RNATE FUNCTION ARCHITECTURE                 |    |

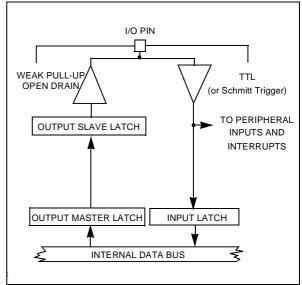

|     |     | 6.5.1 | Pin Declared as I/O                         |    |

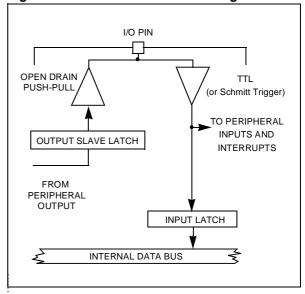

|     |     |       | Pin Declared as an Alternate Function Input |    |

## Table of Contents —

|     | 6.6  | I/O STA | ATUS AFTER WFI, HALT AND RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73         |

|-----|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 7 ( | ON-C | HIP PE  | RIPHERALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74         |

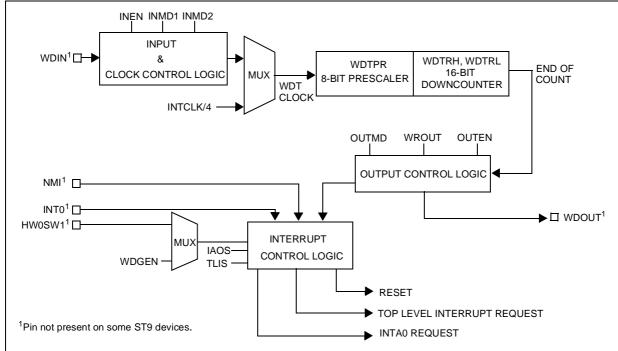

|     | 7.1  | TIMER   | /WATCHDOG (WDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74         |

|     |      | 7.1.1   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 74         |

|     |      |         | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

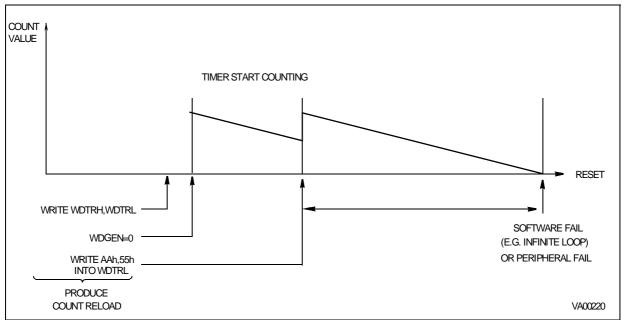

|     |      | 7.1.3   | Watchdog Timer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76         |

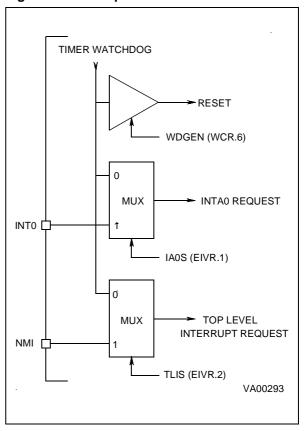

|     |      | 7.1.4   | WDT Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78         |

|     |      |         | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

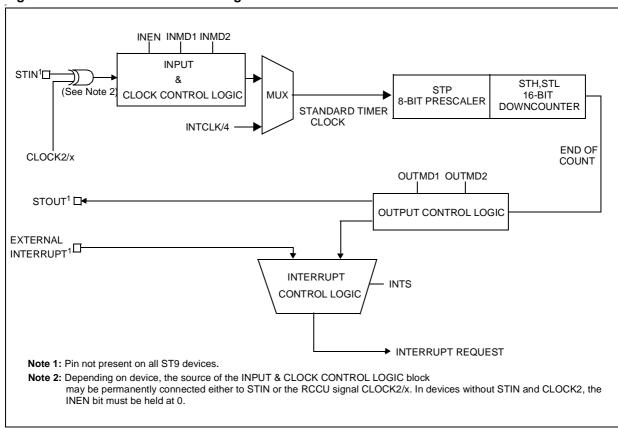

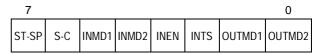

|     | 7.2  | STAND   | DARD TIMER (STIM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 81       |

|     |      | 7.2.1   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 81         |

|     |      |         | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|     |      |         | Interrupt Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|     |      |         | Register Mappingl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|     |      |         | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

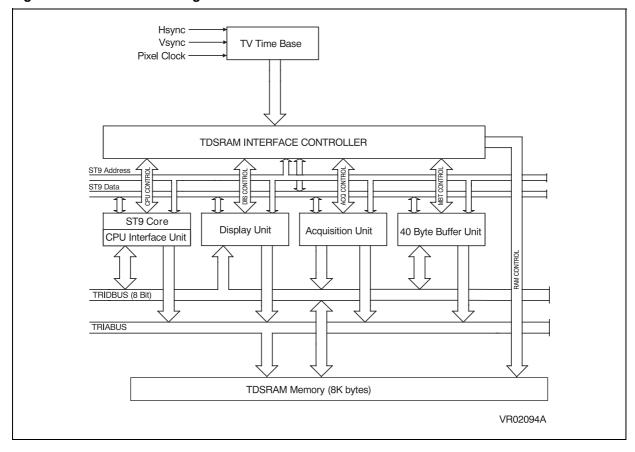

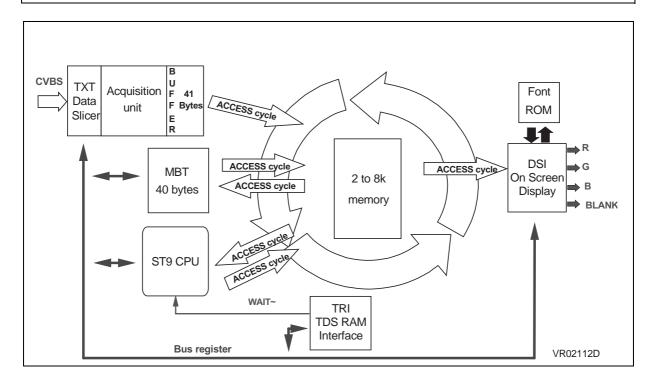

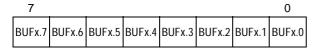

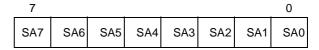

|     | 7.3  |         | EXT DISPLAY STORAGE RAM INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|     |      |         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|     |      |         | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|     |      |         | Initialisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|     | 7 /  |         | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|     | 7.4  |         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|     |      |         | General Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

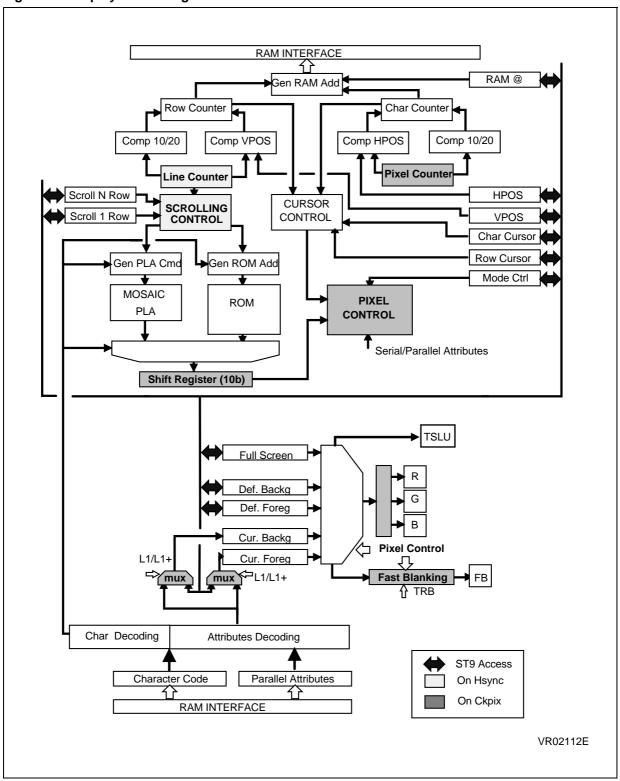

|     |      |         | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|     |      |         | Programming the Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

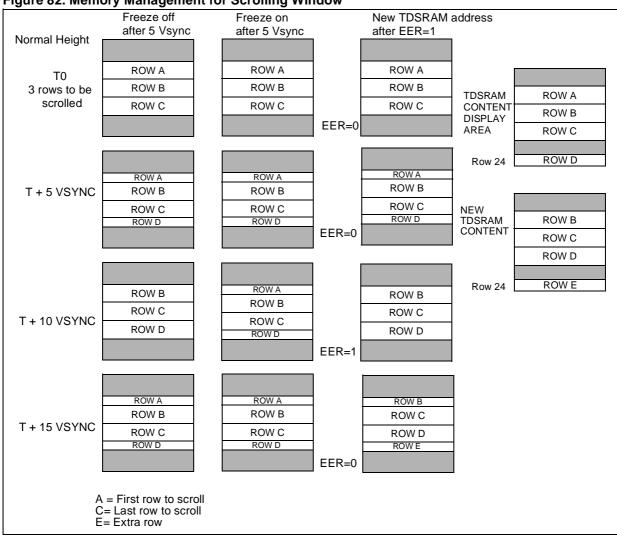

|     |      |         | Vertical Scrolling Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

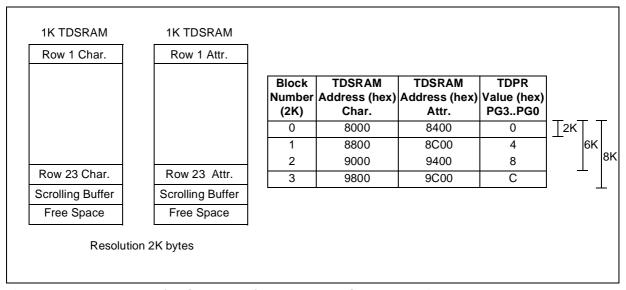

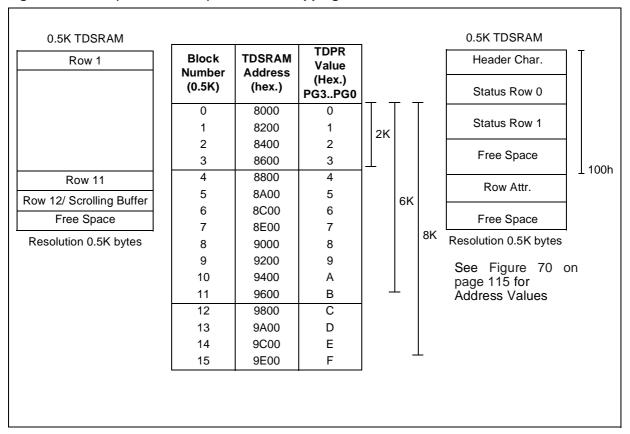

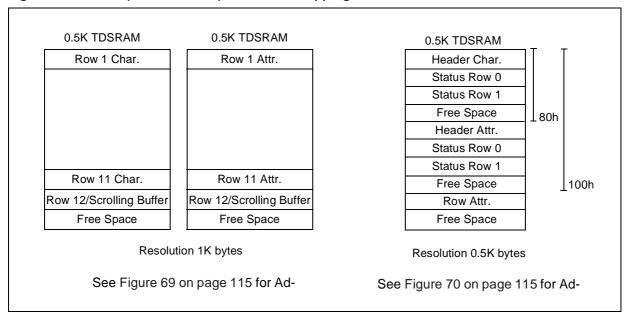

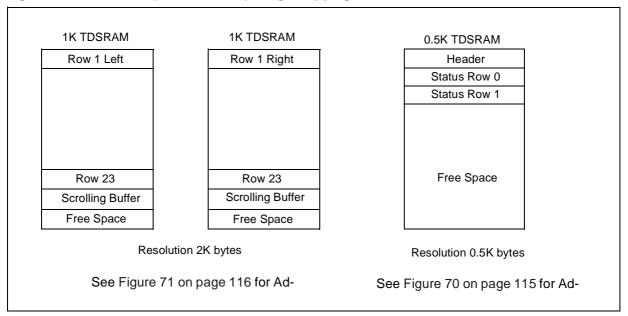

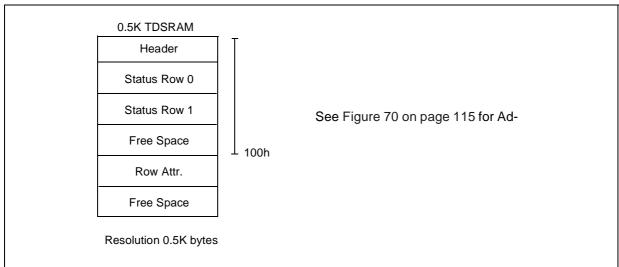

|     |      |         | Display Memory Mapping Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

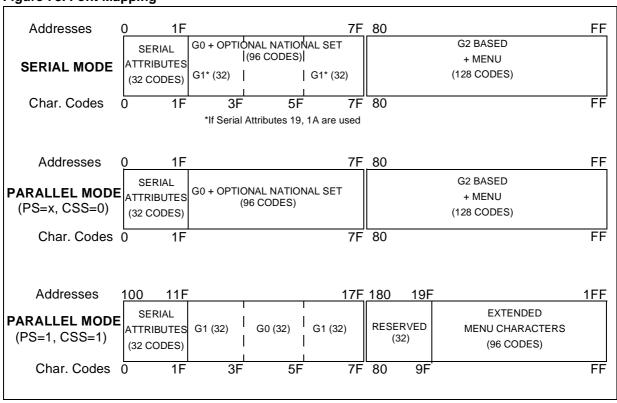

|     |      |         | Font Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|     |      |         | Font Mapping Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

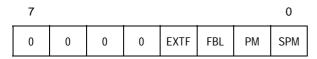

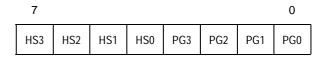

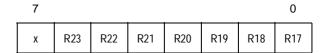

|     |      |         | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

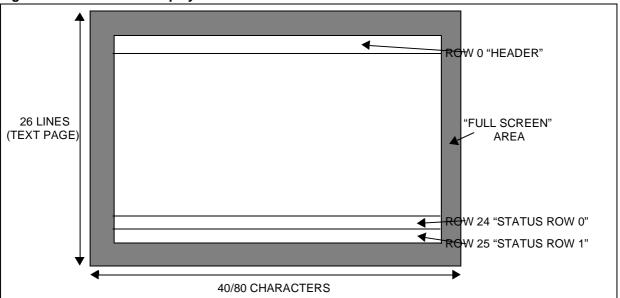

|     |      |         | Application Software Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

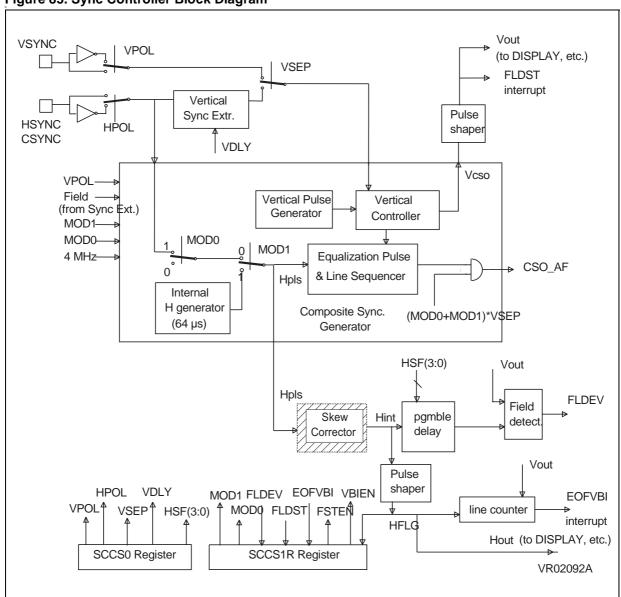

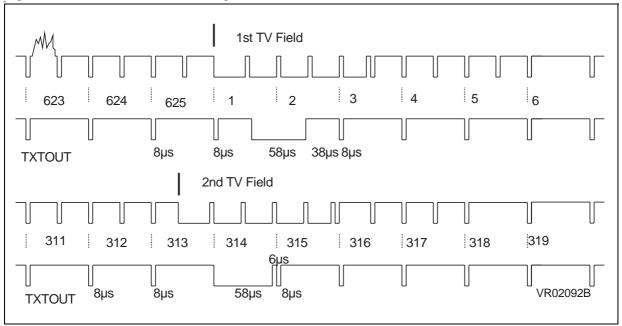

|     | 7.5  | SYNC    | CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 139        |

|     |      | 7.5.1   | H/V Polarity Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 140        |

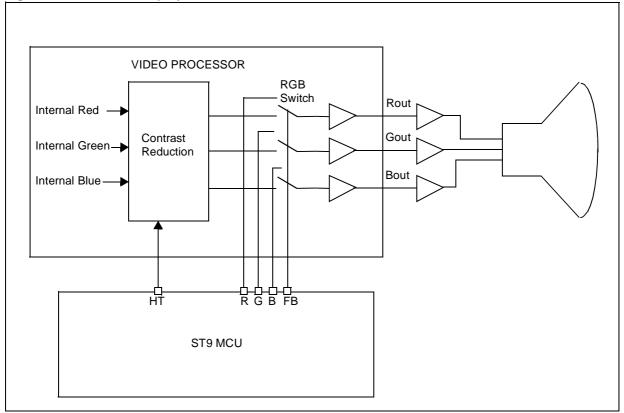

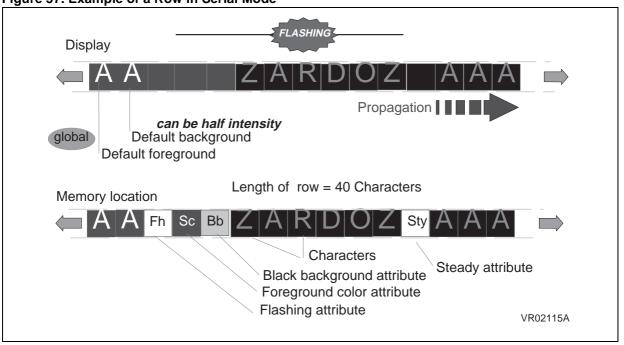

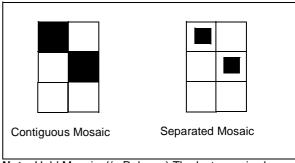

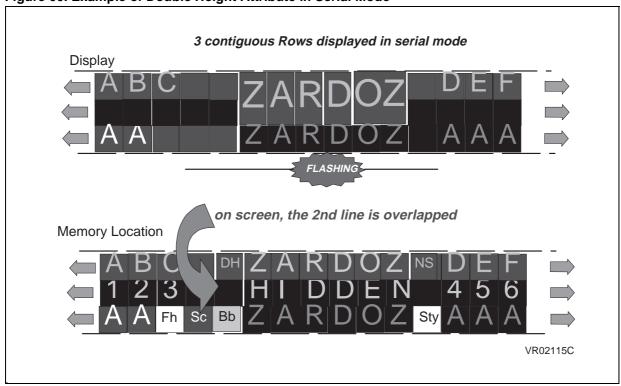

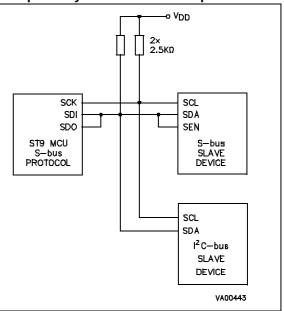

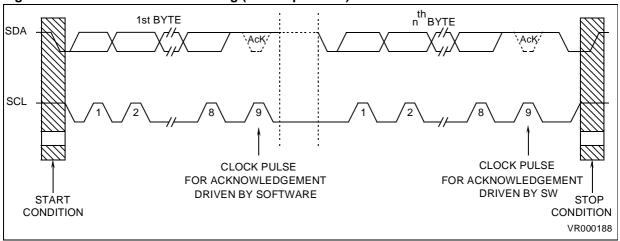

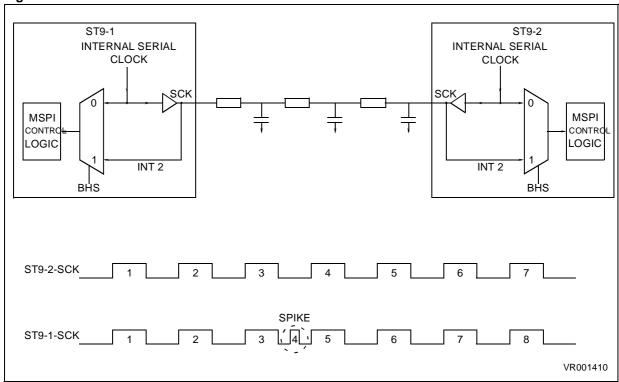

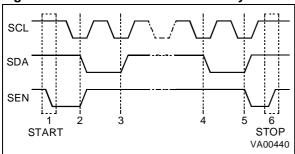

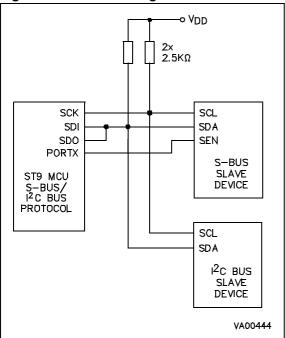

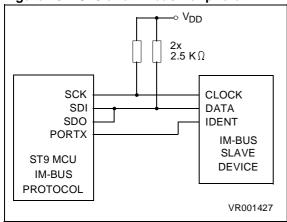

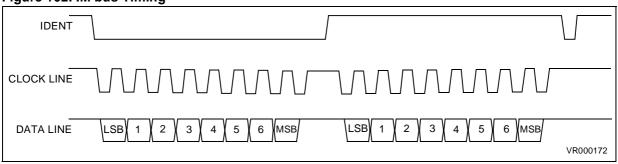

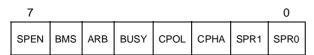

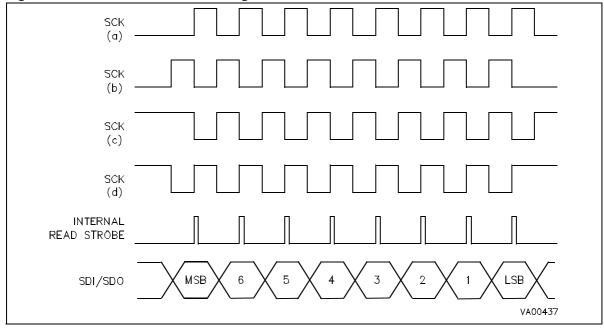

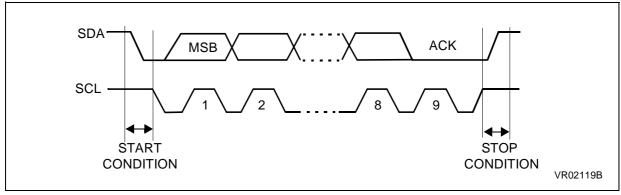

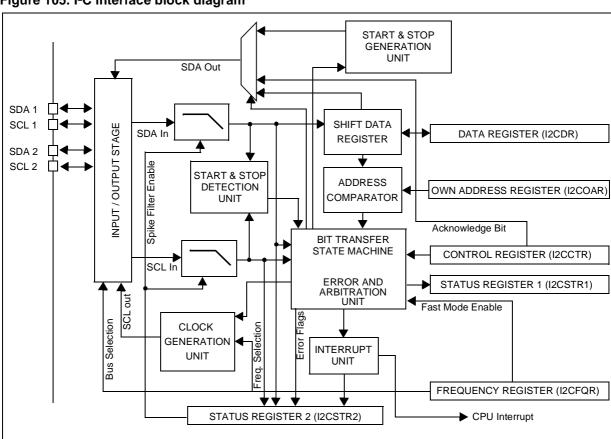

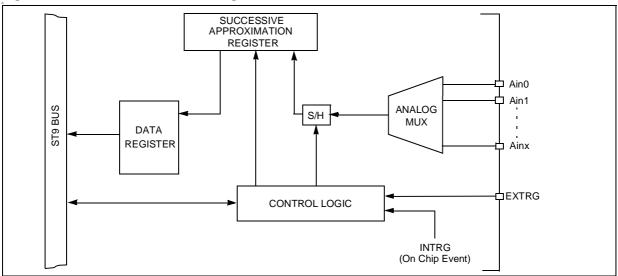

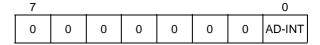

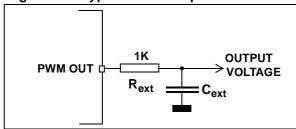

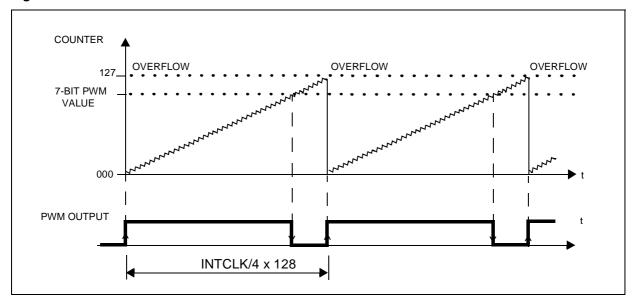

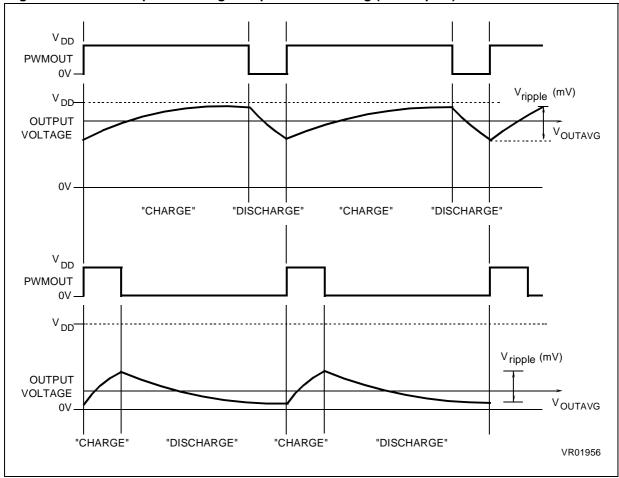

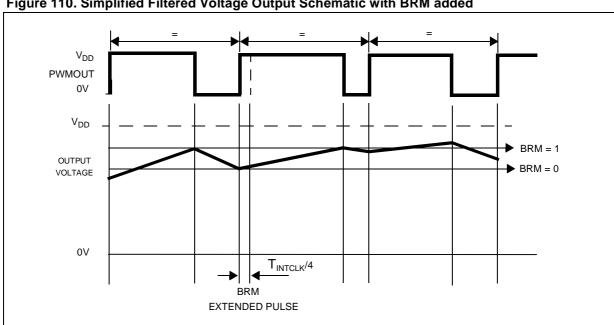

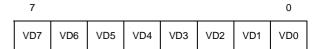

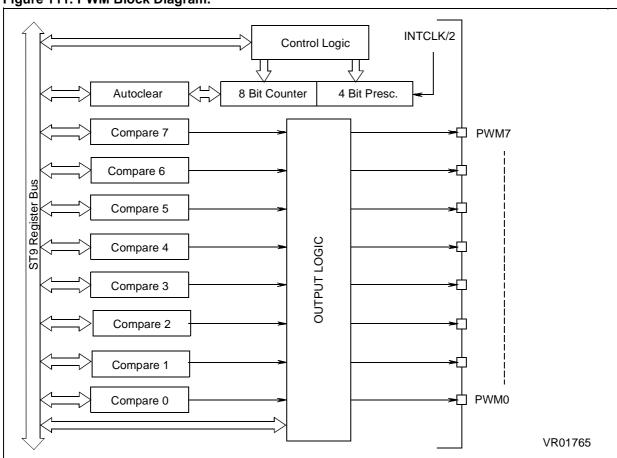

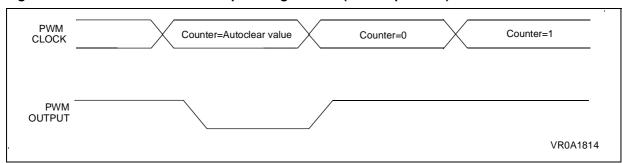

|     |      | 7.5.2   | Field Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 140        |