## **SIEMENS**

## TV Stereo Tone Control IC with Quasi-Stereo Section, Channel 1/2 Switch, SCART Input, and I<sup>2</sup>C Bus Control

**TDA 6200**

Preliminary Data Bipolar IC

#### **Features**

- Treble, bass, balance, and volume control by means of an integrated digital-to-analog converter

- Quasi-stereo circuit during mono operation

- Stereo basewidth expansion during stereo operation

- Physiological volume control

- Channel 1/2 switch-over during dual audio transmission

- SCART connection

- Control of all functions via the I<sup>2</sup>C bus and the bidirectional 4 level line of the TDA 6600-2 (stereo demodulator IC)

- LED driver

- Volume control range 80 dB

- Treble, bass control ± 12 dB

- Channel separation min. 60 dB, cross-talk rejection min. 60 dB

- Parasitic voltage spacing up to 78 dB

| Туре     | Ordering Code | Package  |  |

|----------|---------------|----------|--|

| TDA 6200 | Q67000-A2461  | P-DIP-28 |  |

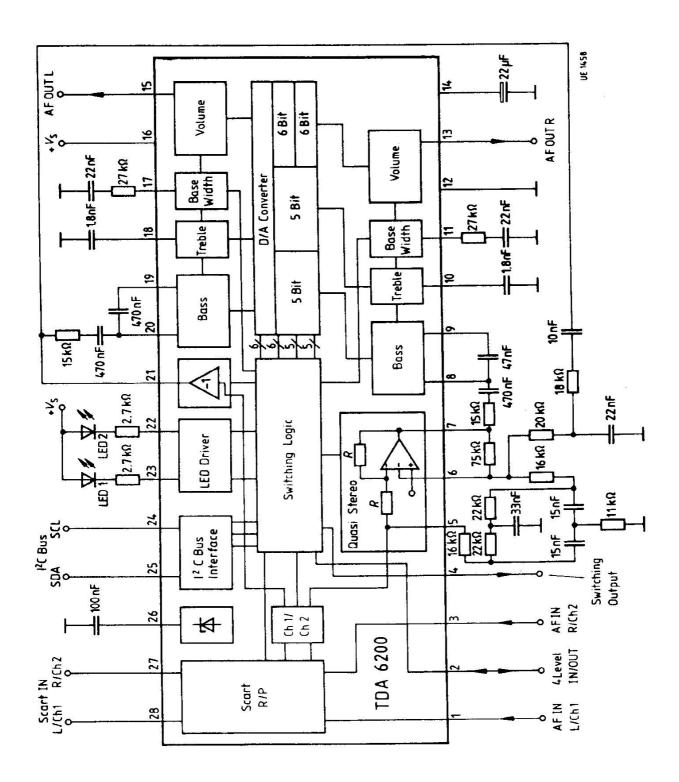

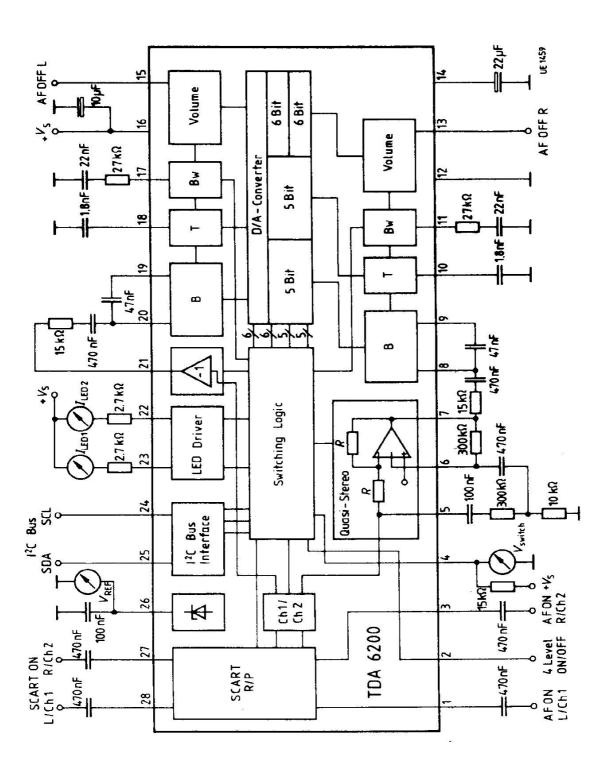

The TDA 6200 is comprised of a SCART switch-over, channel 1/2 switch-over, quasistereo circuit, stereo basewidth expansion, physiological volume control, a treble, bass, and volume control of the injected AF signals as well as an LED driver. The IC is controlled by means of an I<sup>2</sup>C bus serial interface as well as by the bidirectional 4 level line from the TDA 6600-2. The component is used for AF sound signal processing in stereo TV sets.

632 01.90

#### **Circuit Description**

#### The monolithically integrated circuit is comprised of three sections:

- 1. AF input analog switch for SCART and channel 1/2 switch-over

- 2. Sound and volume control with quasi-stereo, physiology and stereo basewidth expansion section

- 3. Control section including the I<sup>2</sup>C bus, 4 level line and digital-to-analog converter

- A two-channel AF analog switch is used to switch from standard TV operation to the SCART playback mode. An additional analog switch is applied for the channel 1/2 switch-over during multichannel transmission. During standard TV operations, this switch will be functional during two-channel transmission and/or SCART playback if the Kbit has been set accordingly.

- 2. The quasi-stereo section in the signal path is applied to generate an acoustic sound impression similar to stereo during the mono signal. This circuitry section is comprised of one op amplifier per channel. While one amplifier is provided with an internally regulated gain factor of 1, the second amplifier can be switched between a gain factor of 1 and a freely selectable gain factor provided by means of external components. The quasi-stereo effect is achieved by forwarding two different types of signals to the input of the second amplifier. While a standard phase AF signal is forwarded via an external band stop filter, a phase inverted signal is forwarded via an external band filter. The attenuation of these networks is compensated by the op amplifier. The result is the generation of a largely amplitude-linear signal, however, turned by 180° in its phase during medium frequencies. This section of the circuit can be switched off.

The sound and volume control section is comprised per stereo channel of 3 op amplifiers with electronic potentiometers and/or switches. By using one external capacitor each for the bass and treble control, 31 different levels for emphasis and deemphasis can be set for the bass and treble control during low and/or high frequencies. The subsequent stage enables a switch-controlled expansion of the basewidth. When the basewidth expansion has been switched on, an anti-phase cross-talk of approx. 60% will occur at an input frequency of approx. 300 Hz. The frequency to be applied as well as the percentage of cross-talk are determined by an external RC combination. The volume control, separate for each channel, is comprised of 64 stages each. As a result, the balance control can be realized by using different settings for the channels.

A physiological volume characteristics is achieved by connecting the volume setting with the treble/bass control. For this purpose, the mean value of the two volume control settings is used. The physiology section can be switched off.

Subsequent to the connection of the supply voltage, the AF output voltage will be delayed by a delay circuit until all voltages are stabilized. In this manner, interfering crackling noises are prevented.

3. The integrated circuit is controlled by means of an I²C bus interface and a 4 level line from the stereo decoder TDA 6600-2. Via this line the evaluation circuit of the TDA 6600-2 provides the necessary information with respect to the 3 modes mono, dual audio, and stereo by means of three different DC voltage levels. For a compulsory (manual) mono mode, a fourth DC voltage level in opposite direction can be used by the TDA 6600-2. This DC voltage level is programmed via the I²C bus interface of the TDA 6200. The system clock for the input SCL of the I²C bus interface is provided by the processor. Pin SDA functions as data input. It can also supply the setting of the identification signal decoder established via the 4 level output and/or an acknowledge message.

The data forwarded by the processor are controlled by the I<sup>2</sup>C bus and subsequently filed in registers according to their functions (latch 1-6).

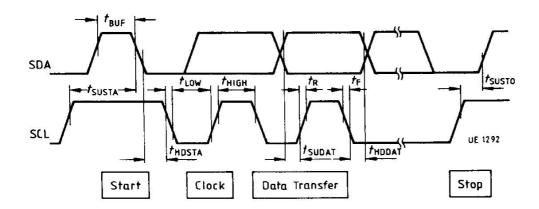

If the bus is free (t off time), both lines will be in the marking state (SDA, SCL are HIGH). Each message begins with the start conditions of SDA returning into LOW, while SCL remains HIGH. All additional information transfer takes place during SCL = LOW, and the data is forwarded to the control with the positive clock edge. However, if SDA returns to HIGH, while SCL is in HIGH, the message is ended since the circuit acknowledges a stop condition.

The logic functions according to the tables on pages 643-645. All messages are transmitted byte-by-byte, followed by a 9th clock pulse, while the control returns the SDA line to LOW (acknowledge condition). In the read mode, the processor transmits the acknowledge bit (will not be checked by the tone control). The first byte is comprised of 7 address bits used by the processor to select the tone control among several peripheral components (chip select). The 8. bit establishes the direction of the subsequent data flow (read/write bit). The 1. and 2. bit of the data bytes determine which latch will be called up (sub-address).

The volume information is set with 6 bits (64 positions); the treble and bass control with 5 bits of which the 1. bit (4. bit of the byte) is the sign bit. The 4 bits of the digital-to-analog converter provide 31 different setting levels. The two volume bytes (left, right) and/or treble and bass bytes have to be transmitted in successive order, since they have the same sub-address. The two bytes for the switching function are subdivided into an AF setting byte and a byte for the operation of the SCART jack.

If the R/W bit = 1 is set during chip addressing, the  $I^2C$  bus operates in the transmission mode. The momentary position of the stereo decoder (corresponds with the status of the 4 level line) is transmitted.

The two LED driver outputs enable the display of stereo, mono or dual audio transmission and/or the SCART playback mode.

## **Block Diagram**

## **Pin Functions**

| Pin No. | Function                                                                                                                                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | AF input for signal from matrix section of TDA 6600-2                                                                                                                 |

| 2       | Bidirectional 4 level control line between TDA 6200 and TDA 6600 used to transmit information with respect to dual audio, mono, stereo and compulsory mono mode       |

| 3       | AF input for signal from matrix section of TDA 6600-2                                                                                                                 |

| 4       | Switching output to control additional functions (open collector), in turn controlled via I <sup>2</sup> C bus                                                        |

| 5       | Low-impedance output to control the quasi-stereo network                                                                                                              |

| 6       | Inverted input of the quasi-stereo op                                                                                                                                 |

| 7       | Low-impedance output of quasi-stereo op, controls bass control                                                                                                        |

| 8, 9    | Connections for external capacitor for right bass control $f_{-3 \text{ dB}} \sim 1/C_{8,9}$                                                                          |

| 10      | Connection for external capacitor for right treble control $f_{-3 \text{ dB}} \sim 1/C_{10}$                                                                          |

| 11      | Connection for network of stereo basewidth expansion percentage of cross- talk ~ $1/R_{11}$ $f_{-3 \text{ dB}} = \frac{1}{2 \pi C_{11} (R_{11} + 1 \text{ k}\Omega)}$ |

| 12      | $2\pi C_{11} (R_{11} + 1 K\Omega)$ GND                                                                                                                                |

| 13      |                                                                                                                                                                       |

| 14      | AF output right (emitter follower)  Decoupling for internal DC operation points. Capacitor also determines the                                                        |

| 15      | duration of the switch-on delay when connecting $V_{16}$ .                                                                                                            |

| 300 T   | AF output left (emitter follower)                                                                                                                                     |

| 16      | Supply voltage                                                                                                                                                        |

| 17      | Connection for network of stereo basewidth expansion percentage of cross- talk ~ $1/R_{17}$ $f_{-3 \text{ dB}} = \frac{1}{2 \pi C_{17} (R_{17} + 1 \text{ k}\Omega)}$ |

| 18      | Connection for external capacitor of left treble control $f_{-3 \text{ dB}} \sim 1/C_{18}$                                                                            |

| 19, 20  | Connections for external capacitor of left bass control $f_{-3 \text{ dB}} \sim 1/C_{19, 20}$                                                                         |

| 21      | Low-impedance output to control the quasi-stereo network and the left bass control                                                                                    |

| 22      | LED driver output for LED 2 (open collector with current limiter)                                                                                                     |

| 23      | LED driver output for LED 1 (open collector with current limiter)                                                                                                     |

| 24      | Clock frequency input of I <sup>2</sup> C bus control (Inter-IC)                                                                                                      |

| 25      | Data input/output of I <sup>2</sup> C bus control                                                                                                                     |

| 26      | Reference voltage of typ. 6 V                                                                                                                                         |

| 27      | AF input of SCART interface                                                                                                                                           |

| 28      | AF input of SCART interface                                                                                                                                           |

## **Absolute Maximum Ratings**

| Parameter                       | Symbol               | Li   | Limit Values   |     |  |  |

|---------------------------------|----------------------|------|----------------|-----|--|--|

|                                 |                      | min. | max.           |     |  |  |

| Supply voltage                  | Vs                   | 0    | 16             | V   |  |  |

| Reference current               | I <sub>26</sub>      | 0    | 2              | mA  |  |  |

| DC voltage                      | V <sub>1, 2, 3</sub> | 0    | <b>V</b> s     | V   |  |  |

| DC voltage                      | V 6, 8, 9            | 0    | <b>V</b> s     | V   |  |  |

| DC voltage                      | V 10, 14, 18         | 0    | <b>V</b> s     | V   |  |  |

| DC voltage                      | V 19, 20, 22         | 0    | V <sub>s</sub> | V   |  |  |

| DC voltage                      | V 23, 24, 25         | 0    | V <sub>S</sub> | V   |  |  |

| DC voltage                      | V 27, 28             | 0    | <b>V</b> s     | V   |  |  |

| DC current                      | 14, 5, 7             | 0    | 2              | mA  |  |  |

| DC current                      | I 11, 13, 15         | 0    | 2              | mA  |  |  |

| DC current                      | I 17, 21             | 0    | 2              | mA  |  |  |

| Junction temperature            | T <sub>j</sub>       |      | 150            | c   |  |  |

| Storage temperature range       | Tstg                 | - 40 | 125            | ,C  |  |  |

| Thermal resistance (system-air) | R th SA              |      | 60             | K/W |  |  |

|                                 | ·                    |      |                |     |  |  |

## **Operating Range**

| Supply voltage      | Vs | 8 | 15.75 | V   |  |

|---------------------|----|---|-------|-----|--|

| Ambient temperature | TA | 0 | 70    | °C  |  |

| Input frequency     | fi | 0 | 20    | kHz |  |

## Characteristics

$Vs = 15 \text{ V}; TA = 25 ^{\circ}\text{C}$

| Parameter                                                               | Symbol            | 1         | _imit Val | ues  | Unit | Test Condition                                           |  |

|-------------------------------------------------------------------------|-------------------|-----------|-----------|------|------|----------------------------------------------------------|--|

|                                                                         |                   | min. typ. |           | max. |      |                                                          |  |

| Current consumption                                                     | <i>I</i> 16       |           | 55        | 80   | mA   | LEDs OFF                                                 |  |

| Reference voltage                                                       | V 26              | 5.4       | 6         | 6.6  | V    |                                                          |  |

| Max. gain  AF input/AF output  L byte = BF;  KL <sup>2)</sup> byte = C0 | G max             | -2        | 0         | 2    | dB   | SC = 0; phys = 0;<br>RK <sup>1)</sup> = 0;<br>Q-S/Bw = 0 |  |

| SCART input/ AF output L byte = BF; KL byte = C0                        | G max             | -2        | 0         | 2    | dB   | SC = 1; phys = 0;<br>RK = 0;<br>Q-S/Bw = 0               |  |

| Min. gain AF input/AF output L byte = 80; KL byte = C0                  | G min             |           |           | - 80 | dB   | SC = 0; phys = 0;<br>RK = 0;<br>Q-S/Bw = 0               |  |

| SCART input/<br>AF output<br>L byte = 80;<br>KL byte = C0               | <i>G</i> min      |           |           | - 80 | dB   | SC = 1; phys = 0;<br>RK = 0;<br>Q-S/Bw = 0               |  |

| Wow and Flutter L-R                                                     | Δa <sub>L-R</sub> |           |           | -2   | dB   |                                                          |  |

| Bass emphasis*) KL byte = C0 + DF                                       | Gв тах            | 9         | 12        |      | dB   | fi = 40 Hz                                               |  |

| Bass deemphasis<br>KL byte = C0 + CF                                    | GB min            |           | - 12      | - 10 | dB   | fi = 40 Hz                                               |  |

| Treble emphasis*) KL byte = DF + C0                                     | G $	au$ max       | 8.5       | 12        |      | dB   | fi = 15 Hz                                               |  |

| Treble deemphasis KL byte = CF + C0                                     | GT min            |           | - 12      | - 10 | dB   | fi= 15 Hz                                                |  |

| Input voltage*)<br>SCART, AF                                            | Vı rms            | 1         |           |      | V    | any KL byte                                              |  |

| Input voltage*)<br>SCART, AF                                            | Vi rms            | 3.5       |           |      | V    | KL byte = CX                                             |  |

| Permissible gain quasi-stereo op                                        | G 7/6             |           |           | 30   | dB   | Q-S/Bw = 1                                               |  |

| Channel separation                                                      | aL-R              | 60        |           |      | dB   | Q-S/Bw = 0; RK = 0                                       |  |

| Antiphased cross talk with basewidth ON                                 | CT <sub>L-R</sub> | 45        | 60        | 75   | %    | stereo; RK = 1                                           |  |

<sup>\*)</sup> refer to page 641

¹) RK ≡ room accustics

²) KL ≡ tone

## Characteristics (cont,d) Vs = 15 V; $T_A = 25 \text{ °C}$

| Parameter                                                          | Symbol                           | L               | imit Val- | ues               | Unit          | <b>Test Condition</b>                                        |  |

|--------------------------------------------------------------------|----------------------------------|-----------------|-----------|-------------------|---------------|--------------------------------------------------------------|--|

|                                                                    |                                  | min. typ.       |           | max.              |               |                                                              |  |

| Cross-talk rejection<br>SCART switch                               | a AF/SF                          | 60              |           |                   | dB            | <i>V</i> <sub>1</sub> rms = 2 V                              |  |

| Ch1/Ch2 switch                                                     | <i>a</i> CH 1/2                  | 60              |           |                   | dB            | V <sub>1</sub> rms = 2 V;<br>dual audio                      |  |

| Total harmonic distortion                                          | THD 13/15                        |                 |           | 1                 | %             | any KL¹) byte<br>Vı rms = 1 V                                |  |

| Total harmonic distortion DIN 45 500*)                             | THD 13/15                        |                 | 0.3       | 0.6               | %             | KL byte = CX;<br>$V_1 \text{ rms} = 1 \text{ V}$             |  |

| Disturbance voltage<br>spacing<br>fi = 20 Hz – 20 kHz              | as/N                             |                 |           | 78                | dB            | DIN 45 405;<br>V:rms = 1 V<br>L byte = BF;<br>KL byte = C0   |  |

| Disturbance voltage at output $f = 20 \text{ Hz} - 20 \text{ kHz}$ | as/n                             |                 | 120       | 150<br>50         | μV<br>μV      | L byte = BF;<br>KL byte = C0<br>L byte = AC;<br>KL byte = C0 |  |

|                                                                    |                                  |                 | 10        | 20                | μV            | L byte = C0<br>L byte = 94;<br>KL byte = C0                  |  |

| Noise voltage<br>CCIR DIN 45 405                                   | $V_n$                            |                 |           | 650               | μV            | L byte = BF<br>KL byte = DF + C                              |  |

| Deviation in amplitude when tone control is in linear position     | $\Delta G$                       |                 | ± 0.5     | ± 1.5             | dB            | KL byte = C0<br>fi = 40 Hz - 15 kH                           |  |

| Volume decontrol for max. phys.                                    | VQ/VI                            |                 | - 30      |                   | dB            | phys = 1                                                     |  |

| Attenuation during<br>MUTE mode                                    | амите                            | 80              |           |                   | dB            | M1 = 1                                                       |  |

| Switching output                                                   | V40N<br>I4 OFFf                  |                 |           | 0.5<br>1          | V<br>μA       | IL = 1 mA                                                    |  |

| LED driver                                                         | I 22, 23<br>V 22, 23<br>I 22, 23 |                 |           | 7.5<br>1.5<br>50  | mA<br>V<br>μA | LED ON<br><i>I</i> 22/23 = 7.5 mA<br>LED OFF                 |  |

| 4 level line<br>Input voltage                                      | V12<br>V12<br>V12                | 0<br>2.4<br>5.2 |           | 1.8<br>3.9<br>6.6 | V<br>V        | recognizes mono<br>recognizes dual<br>recognizes stereo      |  |

| Input current                                                      | $V_{12}$                         |                 |           | 3                 | μА            |                                                              |  |

| Compulsory mono                                                    | V <sub>Q2</sub>                  |                 |           | 0.2               | V             | $M2 = 1; I_2 = 1 \text{ mA}$                                 |  |

<sup>\*)</sup> refer next page

<sup>1)</sup> KL ≡ tone

## Characteristics (cont,d) $V_S = 15 \text{ V}$ ; $T_A = 25 \text{ °C}$

| Parameter                                                   | Symbol                              |            | alues | Unit      |                          |

|-------------------------------------------------------------|-------------------------------------|------------|-------|-----------|--------------------------|

|                                                             |                                     | min.       | typ.  | max.      | 2000                     |

| <sup>2</sup> C Bus (SCL, SDA)                               |                                     |            |       |           |                          |

| SCL, SDA Edges                                              |                                     |            |       |           |                          |

| Rise time                                                   | <i>t</i> R                          |            |       | 1         | μS                       |

| Fall time                                                   | t F                                 |            |       | 0.3       | μS                       |

| Shift Register Clock Pulse S                                | CL                                  | 1000       |       |           |                          |

| Frequency                                                   | fscL                                | 0          |       | 100       | kHz                      |

| H-pulse width                                               | <i>t</i> HIGH                       | 4          |       |           | μS                       |

| L-pulse width                                               | tLOW                                | 4          |       |           | μS                       |

| Start                                                       |                                     |            |       |           |                          |

| Set-up time                                                 | <i>t</i> susta                      | 4          |       |           | μS                       |

| Hold time                                                   | t HDSTA                             | 4          |       |           | μS                       |

| Stop                                                        |                                     |            |       |           |                          |

| Set-up time                                                 | <i>t</i> susto                      | 4          |       | 1990      | μS                       |

| Bus free time                                               | <i>t</i> BUF                        | 4          |       |           | μS                       |

| DataTransfer                                                |                                     | 93562.20   | 52 98 |           |                          |

| Set-up time                                                 | <i>t</i> SUDAT                      | 1          |       |           | μS                       |

| Hold time                                                   | <i>t</i> HDDAT                      | 1          |       |           | μS                       |

| nputs SCL, SDA                                              |                                     |            |       |           |                          |

| Input voltage                                               | $oldsymbol{V}$ ін $oldsymbol{V}$ іL | 2.4<br>0.3 |       | 5.5<br>1  | V<br>V                   |

| Input current                                               | IIH<br>IIL                          |            |       | 50<br>100 | μ <b>Α</b><br>μ <b>Α</b> |

| Output SDA (open collector)                                 | ·                                   |            |       |           |                          |

| Output voltage                                              | V <sub>Q</sub> H                    |            | 1     | 5.5       | V                        |

| $R_L = 2.5 \text{ k}\Omega$ ; $I_{\Omega L} = 2 \text{ mA}$ | $V_{QL}$                            | l l        |       | 0.4       | V                        |

The data marked with an asterisk\*) depend on the supply voltage. With lower  $V{\rm s}$  the input voltage decreases accordingly.

## Characteristics

Vs = 15 V; TA = 25 °C

| min. typ. max.                                 |    |

|------------------------------------------------|----|

|                                                |    |

| Design-Related Characteristics                 |    |

| Input impedance SCART R <sub>1 27, 28</sub> 35 | kΩ |

| Input impedance AF R <sub>11,3</sub> 35        | kΩ |

| Output impedance Ros, 7, 21 200                | Ω  |

| Output impedance AF output RQ 13, 15 200       | Ω  |

| Internal resistance Bw R <sub>111,17</sub> 1   | kΩ |

#### **Measurement Circuit**

## I<sup>2</sup>C Bus Timing Diagram

tsusta Set-up time (start)

thdsta Hold time (start)

thigh Pulse width (clock)

thou Pulse width (clock)

tsudat Set-up time (data transfer)

thddat Hold time (data transfer)

tsusto Set-up time (stop)

t BUF Bus free time

t<sub>F</sub> Fall time t<sub>R</sub> Rise time

The listed times are referenced to the  $V \Vdash$  and  $V \Vdash$  values.

| Softwar | e |

|---------|---|

|---------|---|

The following data format is used:

#### 1) Chip Address

#### 2) Data Bytes with Sub-Addresses

#### a) Volume

| MSB                                                      |   |     |     |     |     |     | LSB |          |

|----------------------------------------------------------|---|-----|-----|-----|-----|-----|-----|----------|

| 1                                                        | 0 | V05 | V04 | V03 | V02 | V01 | V00 | (left) + |

| 1                                                        | 0 | V15 | V14 | V13 | V12 | V11 | V10 | (right)  |

| The two bytes are always transmitted in successive order |   |     |     |     |     |     |     |          |

$$V \times 5 = MSB$$

$V \times 0 = LSB$

#### b) Tone

| MSB |   |   |    |    |    |    | LSB |   |

|-----|---|---|----|----|----|----|-----|---|

| 1   | 1 | X | HV | НЗ | H2 | H1 | H0  | + |

| 1   | 1 | X | TV | Т3 | T2 | T1 | T0  |   |

The two bytes are always transmitted in successive order

HV or TV are sign bits

$$H0 \text{ or } T0 = LSB$$

| 1 | 1 | Χ | 0 | 1 | 1 | 1 | 1 | min. treble or bass   |

|---|---|---|---|---|---|---|---|-----------------------|

| 1 | 1 | X | X | 0 | 0 | 0 | 0 | linear treble or bass |

| 1 | 1 | X | 1 | 1 | 1 | 1 | 1 | max. treble or bass   |

#### Software

| C) | AF | set | byte |

|----|----|-----|------|

|    |    |     |      |

| MSB    |     |       |              |                   |         |            | LSB         |                                |

|--------|-----|-------|--------------|-------------------|---------|------------|-------------|--------------------------------|

| 0      | 0   | M1    | M2           | Ch1/2             | RK      | Phys       | Q-S/Bw      |                                |

|        |     |       |              |                   |         |            |             |                                |

| M1     | = 1 | Muti  | ng for       | AF out            | out     |            |             |                                |

| M1     | = 0 | AF C  | _            |                   |         |            |             |                                |

| M2     | = 1 | Com   | pulso        | ry mond           | (via 4  | 4 level li | ne)         |                                |

| M2     | = 0 | Stan  | dard         | operatio          | n for i | dentifica  | ation signa | ıl decoder                     |

| Ch1/2  | = 0 | Duri  | ng du        | al audio          | mode    | e, chann   | el 1 at AF  | output                         |

| Ch1/2  | = 1 | Duri  | ng du        | al audio          | mode    | e, chann   | el 2 at AF  | output                         |

|        |     | (only | activ        | ve with           | dual    | audio v    | ria 4 level | line or during SCART playback  |

|        |     | and   | Kbit =       | : 1)              |         |            |             |                                |

| RK     | = 1 |       |              | and ON;           |         |            |             |                                |

|        |     |       | 95           | _                 |         |            |             | mono and dual audio or stereo  |

|        |     |       |              |                   |         | during     | stereo tra  | ansmission – automatic switch- |

|        |     | No.   | D. CONT. BL. | level lin         | 70      |            |             |                                |

|        |     |       |              | 5 <del>.7</del> 5 |         |            |             | expansion ON                   |

| RK     | = 0 |       |              |                   | •       |            | id quasi-st | ereo OFF                       |

| Phys   | = 1 |       | _            | ical volu         |         |            |             |                                |

| Phys   | = 0 | 700   | 00 00 10     | ical volu         |         |            |             |                                |

| Q-S/Bw | = 1 |       |              |                   |         |            |             | reo basewidth expansion ON     |

|        | _   |       | 0.50         | 9 <del>.5</del> 0 |         |            |             | expansion ON                   |

| Q-S/Bw | = 0 | Qua   | si-ste       | reo and           | stered  | basew      | ridth expar | ision OFF                      |

#### d) SCART set byte

| MSB |     |               |                   |         |         |          | LSB                      |                                      |

|-----|-----|---------------|-------------------|---------|---------|----------|--------------------------|--------------------------------------|

| 0   | 1   | SC            | Sch               | Ch      | X       | X        | X                        |                                      |

| SC  | = 1 |               |                   |         |         | SCAR     | T input cor              | nnected with AF output               |

| SC  | = 0 |               | ndard o           |         |         |          |                          |                                      |

| Sch | = 1 | Swit          | tching o          | utput C | DN (op  | en colle | ector)                   |                                      |

| Sch | = 0 |               |                   |         |         |          | t can e.g.<br>he video s | be used for switch—over from ection) |

| Ch  | = 1 | The second of | back of           |         | RT du   | ıal tran | ismission;               | channel selection via Ch1/2 bit      |

| Ch  | = 0 |               | output<br>smissio | 10.00   | es in s | stereo   | mode. Pla                | ayback of SCART stereo (mono)        |

#### Note:

The AF section is automatically controlled by the 4 level line. Compulsory mono M2 is given priority. After Power-ON-Reset all latches are set at 0 (volume min., tone linear, . . .); only the function Q-S/Bw is set at 1.

#### Software

#### 3) Transmission Mode

requires new chip addressing with R/W bit = 1.

| MSB |   |     |                           |        |        |    | LSB     |  |  |

|-----|---|-----|---------------------------|--------|--------|----|---------|--|--|

| St  | D | X   | X                         | X      | X      | X  | X       |  |  |

| St  | D |     |                           |        |        |    |         |  |  |

| 1   | 1 | Dec | oder re                   | cogniz | es moi | 10 |         |  |  |

| 0   | 1 | Dec | Decoder recognizes stereo |        |        |    |         |  |  |

| 1   | 0 | Dec | oder re                   | cogniz | es dua | l  |         |  |  |

| 0   | 0 |     |                           |        |        |    | ressed) |  |  |

The transmission function is not required for the operation of the IC. Instead this function is used to inform the  $\mu$ C about the status of the identification signal decoder to enable additional functions.

#### **LED Driver**

TV operating mode:

| 4 level line | Ch1/2 bit  | LED 1 | LED 2 |

|--------------|------------|-------|-------|

| Mono         | ×          | OFF   | OFF   |

| Stereo       | ×          | ON    | ON    |

| Dual         | 0          | ON    | OFF   |

| Dual         | 1          | OFF   | ON    |

| SCART play   | back mode: |       |       |

| SC bit | Ch bit | Ch 1/2 bit | LED 1 | LED 2 |

|--------|--------|------------|-------|-------|

| 1      | 0      | X          | ON    | ON    |

| 1      | 1      | 0          | ON    | OFF   |

| 1      | 1      | 1          | OFF   | ON    |

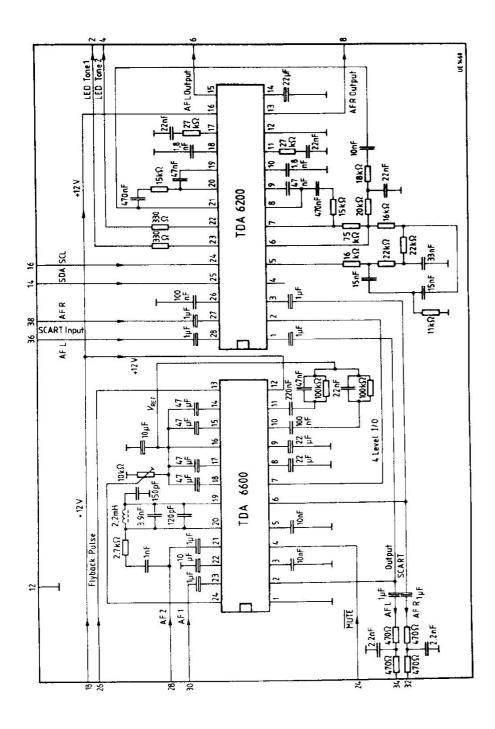

# **Application Circuit Stereo Decoder, Matrix and Tone Control**