## 9-Channel Level Shifter With Gate Voltage Shaping and Discharge Functions

#### **FEATURES**

- 9-Channel Level Shifter Supports 6 x CLK, VST, ODD, and EVEN Signals

- Organized as Two Groups of 7 + 2 Channels

- Separate Positive Supplies (V<sub>GHX</sub>) for Each Group

- V<sub>GHX</sub> Levels up to 38V

- V<sub>GL</sub> Levels Down to -13V

- Panel DISCHARGE Function

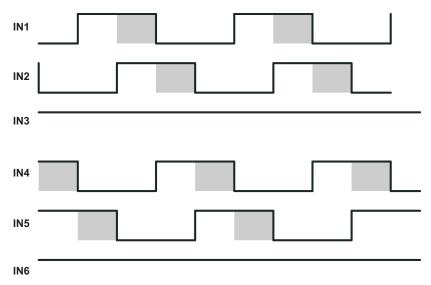

- Suitable for 4-Phase and 6-Phase Applications

- Gate Voltage Shaping on Channels 1 to 6

- Supports Single and Multiple Flicker Clocks

- · Peak Output Currents greater than 500mA

- 28-Pin 5×5 mm QFN Package

#### **APPLICATIONS**

LCD Displays Using Gate-in-Panel (GIP) Technology

#### **DESCRIPTION**

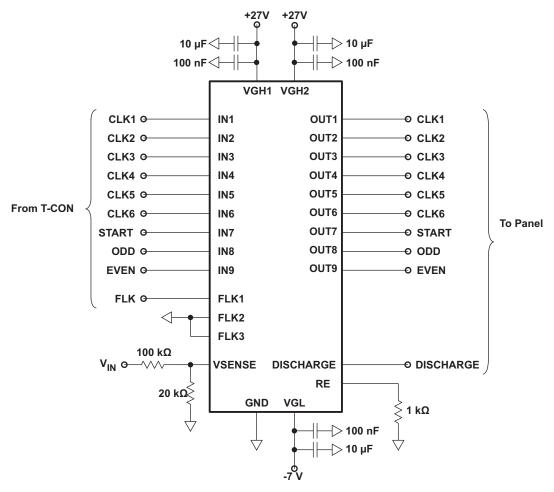

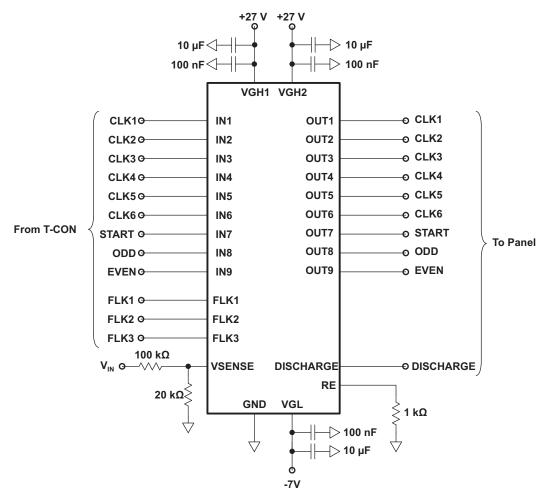

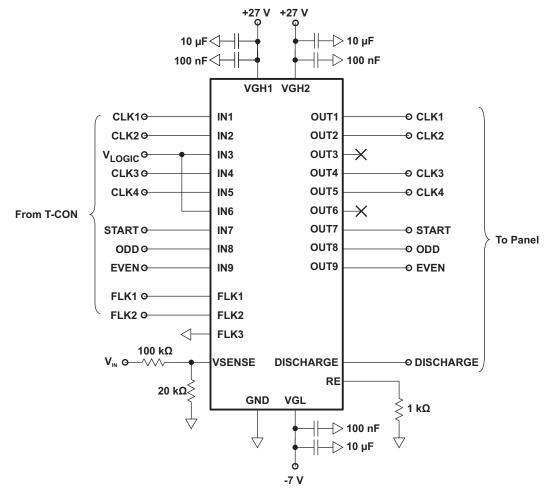

The TPS65192 is a 9 channel level-shifter intended for use in LCD display applications such as TVs and monitors. The device converts the logic-level signals generated by the Timing Controller (T-CON) to the high-level signals used by the display panel.

The 9 level shifter channels are organized as two groups. Channels 1 through 7 are powered from  $V_{GH1}$  and  $V_{GL}$ , and channels 8 and 9 are powered from  $V_{GH2}$  and  $V_{GL}$ . Each level-shifter channel features low impedance output stages that achieve fast rise and fall times even when driving the capacitive loading typically present in LCD display applications.

Level shifter channels 1 through 6 support gate voltage shaping, which can be used to improve picture quality by reducing image sticking. Novel decoding logic enables a single flicker clock signal to control gate voltage shaping for all CLK channels without the need for synchronization. The device also supports the use of multiple flicker clocks. The rate of decay is set by an external resistor or resistor network connected to the RE pin.

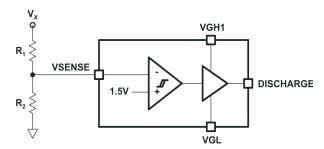

A tenth level shifter channel specially configured with a comparator input stage allows designers to implement panel discharging during power-down.

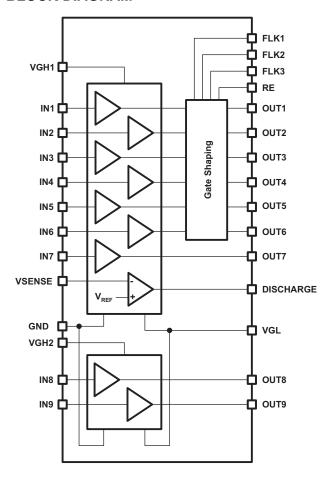

#### **BLOCK DIAGRAM**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION(1)

| T <sub>A</sub> | ORDERING     | PACKAGE    | PACKAGE MARKING |

|----------------|--------------|------------|-----------------|

| -40°C to 85°C  | TPS65192RHDR | 28-Pin QFN | TPS65192        |

<sup>(1)</sup> The device is supplied taped and reeled, with 3000 devices per reel.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                              |                                           | VALUE                 | UNIT     |

|------------------------------|-------------------------------------------|-----------------------|----------|

| Cumply valtage (2)           | VGH1, VGH2                                | -0.3 to 45            | V        |

| Supply voltage (2)           | VGL                                       | 0.3 to -15            | V        |

| Input voltage <sup>(2)</sup> | IN1 through IN9, VSENSE, FLK1, FLK2, FLK3 | -0.3 to 7.0           | V        |

| input voitage -/             | RE                                        | -0.3 to 45            | V        |

| Output current               | RE                                        | 0.1                   | Α        |

| ESD rating                   | HBM                                       | 2                     | kV       |

|                              | MM                                        | 200                   | V        |

|                              | CDM                                       | 700                   | V        |

| Continuous power d           | issipation                                | See Dissipation Ratin | ig Table |

| Operating ambient to         | emperature range                          | -40 to 85             | °C       |

| Operating junction to        | emperature range                          | -40 to 150            | °C       |

| Storage temperature          | e range                                   | -65 to 150            | °C       |

| Lead temperature (s          | oldering, 10 sec)                         | 300                   | °C       |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATINGS**

| PACKAGE                   | $\theta_{JA}$ | T <sub>A</sub> ≤25°C<br>POWER RATING | T <sub>A</sub> =70°C<br>POWER RATING | T <sub>A</sub> =85°C<br>POWER RATING |

|---------------------------|---------------|--------------------------------------|--------------------------------------|--------------------------------------|

| 28-Pin QFN <sup>(1)</sup> | 35°C/W        | 3.57W                                | 2.29W                                | 1.86W                                |

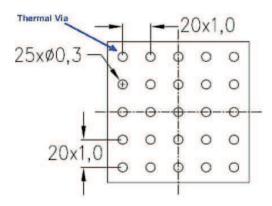

<sup>(1)</sup> This data is based on using a JEDEC High-K board with the exposed die pad connected to a Cu pad on the board connected to the ground plane by a 2x3 thermal via matrix.

#### RECOMMENDED OPERATING CONDITIONS

|                                     |                                | MIN | TYP | MAX | UNIT |

|-------------------------------------|--------------------------------|-----|-----|-----|------|

| V <sub>GH1</sub> , V <sub>GH2</sub> | Positive supply voltage range  | 12  | 30  | 38  | V    |

| $V_{GL}$                            | Negative supply voltage range  | -13 | -7  | -2  | V    |

| T <sub>A</sub>                      | Operating ambient temperature  | -40 |     | 85  | °C   |

| T <sub>J</sub>                      | Operating junction temperature | -40 |     | 125 | °C   |

Product Folder Link(s): TPS65192

<sup>(2)</sup> All voltage values are with respect to the GND pin.

#### **ELECTRICAL CHARACTERISTICS**

$V_{GH1} = V_{GH2} = 30V$ ;  $V_{GL} = -7~V$ ;  $T_A = -40^{\circ}C$  to  $85^{\circ}C$ ; typical values are at  $25^{\circ}C$  (unless otherwise noted).

|                     | PARAMETER                                        | TEST CONDITIONS                                                  | MIN   | TYP   | MAX   | UNIT |

|---------------------|--------------------------------------------------|------------------------------------------------------------------|-------|-------|-------|------|

| POWER S             | SUPPLY                                           |                                                                  |       |       |       |      |

| I <sub>GH1</sub>    | V <sub>GH1</sub> Supply current                  | IN1 to IN7 = GND; V <sub>SENSE</sub> = 0V                        |       | 0.35  | 3     | mA   |

| $I_{GH2}$           | V <sub>GH2</sub> Supply current                  | IN8 and IN9 = GND; V <sub>SENSE</sub> =0V                        |       | 0.012 | 1     | mA   |

| $I_{GL}$            | V <sub>GL</sub> Supply current                   | IN1 to IN9 = GND; V <sub>SENSE</sub> = 0V                        |       | 0.144 | 4     | mA   |

| $V_{\text{UVLO}}$   | Undervoltage lockout threshold                   | V <sub>GH1</sub> rising                                          | 10.5  |       | 13.5  | V    |

| $V_{HYS}$           | Undervoltage lockout hysteresis                  | V <sub>GH1</sub> falling                                         |       | 450   |       | mV   |

| LEVEL S             | HIFTERS                                          |                                                                  |       |       |       |      |

|                     |                                                  | Continuous; OUT1 to OUT7                                         | ±15   |       |       | mA   |

|                     | Output ourropt                                   | Peak; OUT1 to OUT7                                               | ±300  | ±650  |       | IIIA |

| I <sub>OUTX</sub>   | Output current                                   | Continuous; OUT8 and OUT9, DISCHARGE                             | ±15   |       |       | A    |

|                     |                                                  | Peak; OUT8 an OUT9, DISCHARGE                                    | ±150  | ±250  |       | mA   |

|                     | lament annualit                                  | IN1 to IN9 = GND                                                 |       |       | ±1    | ^    |

| I <sub>INX</sub>    | Input current                                    | IN1 to IN9 = 3.3 V                                               |       |       | ±1    | μΑ   |

| V <sub>IH</sub>     | High level input voltage                         | IN1 to IN9                                                       |       |       | 2.0   | V    |

| $V_{IL}$            | Low level input voltage                          | IN1 to IN9                                                       | 0.5   |       |       | V    |

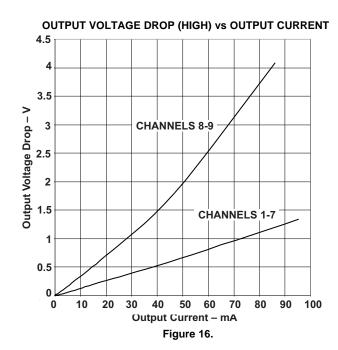

| .,                  | O                                                | OUT1 to OUT7; I <sub>LOAD</sub> = 10 mA                          |       | 0.12  | 0.4   | .,   |

| $V_{DROPH}$         | Output voltage drop high                         | OUT8 and OUT9, DISCHARGE; I <sub>LOAD</sub> = 10 mA              |       | 0.36  | 1.0   | V    |

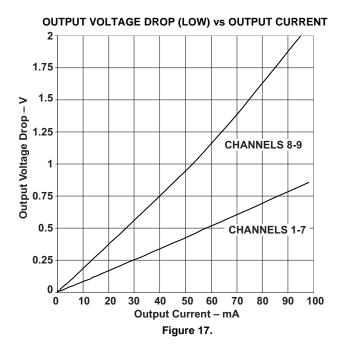

| .,                  | • · · · · · · · · · · · · · · · · · · ·          | OUT1 to OUT7; I <sub>LOAD</sub> = -10 mA                         |       | 0.07  | 0.3   | .,   |

| $V_{DROPL}$         | Output voltage drop low                          | OUT8 and OUT9, DISCHARGE; I <sub>LOAD</sub> = -10 mA             |       | 0.17  | 1.0   | V    |

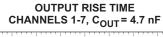

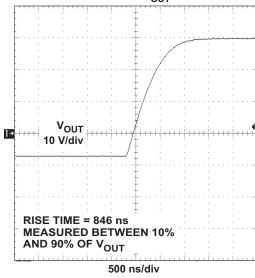

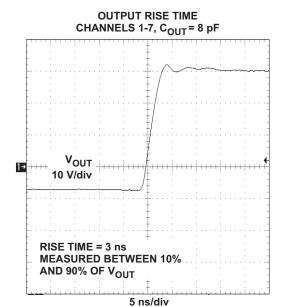

|                     | Diag the s                                       | OUT1 to OUT7; C <sub>LOAD</sub> = 4.7 nF <sup>(1)</sup>          |       | 275   | 520   |      |

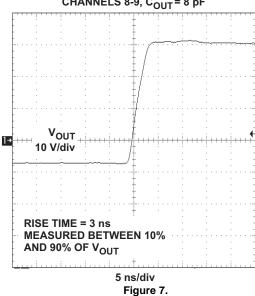

| t <sub>R</sub>      | Rise time                                        | OUT8 and OUT9; C <sub>LOAD</sub> = 4.7 nF <sup>(1)</sup>         |       | 761   | 1000  | ns   |

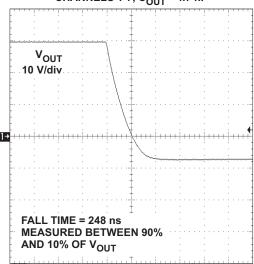

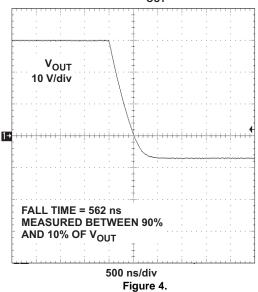

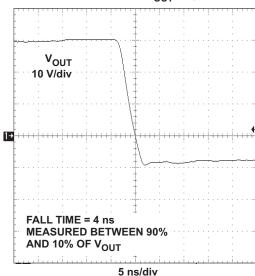

|                     | = ""                                             | OUT1 to OUT7; C <sub>LOAD</sub> = 4.7nF <sup>(1)</sup>           |       | 220   | 370   |      |

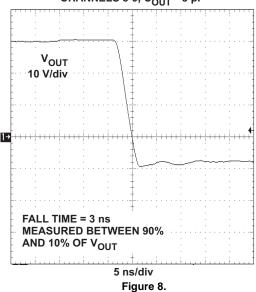

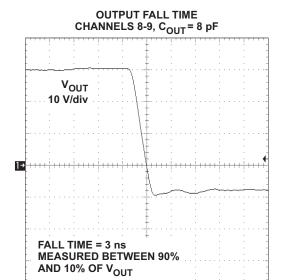

| t <sub>F</sub>      | Fall time                                        | OUT8 and OUT9; C <sub>LOAD</sub> = 4.7 nF <sup>(1)</sup>         |       | 526   | 850   | ns   |

| t <sub>PH</sub>     | Daniel and delay                                 | Rising edge, C <sub>L</sub> = 150 pF                             |       |       | 60    |      |

| t <sub>PL</sub>     | - Propagation delay                              | Falling edge, C <sub>L</sub> = 150 pF                            |       |       | 60    | ns   |

| GATE VC             | DLTAGE SHAPING                                   |                                                                  |       |       |       |      |

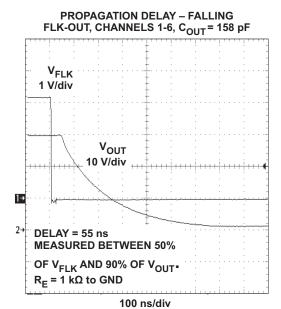

| t <sub>PH</sub>     | Propagation delay – gate voltage shaping enabled | FLK falling                                                      |       |       | 100   | ns   |

| t <sub>SU</sub>     | Set-up time                                      | Time active IN signals must be stable before falling edge of FLK |       |       | 70    | ns   |

| r <sub>DS(on)</sub> | Resistance between OUT and RE pins               |                                                                  |       | 70    | 100   | Ω    |

| I <sub>LEAK</sub>   | Leakage current from RE pin                      |                                                                  |       |       | ±10   | μΑ   |

| DISCHAF             | RGE                                              |                                                                  |       |       | ,     |      |

| V <sub>SENSE</sub>  | Discharge voltage sense threshold                | V <sub>SENSE</sub> falling                                       | 1.275 | 1.5   | 1.725 | V    |

| I <sub>SENSE</sub>  | Discharge voltage sense input current            | V <sub>SENSE</sub> = 2V                                          |       |       | ±1    | μΑ   |

| V <sub>HYS</sub>    | Discharge voltage sense hysteresis               | V <sub>SENSE</sub> rising                                        |       | 40    |       | mV   |

<sup>(1)</sup> Rise and fall times are measured between 10% and 90% of the waveform's amplitude.

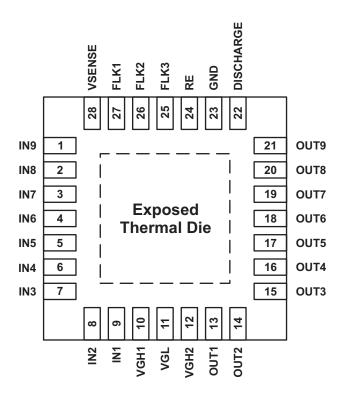

#### **DEVICE INFORMATION**

#### **PIN ASSIGNMENT**

#### **PIN FUNCTIONS**

| PIN       |     |     | DECODINE                                                                                                                                                                       |  |  |  |  |  |

|-----------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME      | NO. | 1/0 | DESCRIPTION                                                                                                                                                                    |  |  |  |  |  |

| IN9       | 1   | I   | Level shifter channel 9 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| IN8       | 2   | I   | Level shifter channel 8 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| IN7       | 3   | I   | Level shifter channel 7 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| IN6       | 4   | I   | Level shifter channel 6 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| IN5       | 5   | I   | Level shifter channel 5 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| IN4       | 6   | I   | Level shifter channel 4 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| IN3       | 7   | I   | Level shifter channel 3 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| IN2       | 8   | I   | Level shifter channel 2 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| IN1       | 9   | I   | Level shifter channel 1 input. Connect this pin to GND, if not used.                                                                                                           |  |  |  |  |  |

| VGH1      | 10  | Р   | Positive supply voltage for level shifter channels 1 through 7 and discharge function. Bypass this pin wit a parallel combination of $10\mu F$ and $100nF$ ceramic capacitors. |  |  |  |  |  |

| VGL       | 11  | Р   | Negative supply voltage. Bypass this pin with a parallel combination of 10μF and 100nF ceramic capacitors.                                                                     |  |  |  |  |  |

| VGH2      | 12  | Р   | Positive supply voltage for level shifter channels 8 and 9. Bypass this pin with a parallel combination of 10µF and 100nF ceramic capacitors.                                  |  |  |  |  |  |

| OUT1      | 13  | 0   | Level shifter channel 1 output. Leave this pin floating, if not used.                                                                                                          |  |  |  |  |  |

| OUT2      | 14  | 0   | Level shifter channel 2 output. Leave this pin floating, if not used.                                                                                                          |  |  |  |  |  |

| OUT3      | 15  | 0   | Level shifter channel 3 output. Leave this pin floating, if not used.                                                                                                          |  |  |  |  |  |

| OUT4      | 16  | 0   | Level shifter channel 4 output. Leave this pin floating, if not used.                                                                                                          |  |  |  |  |  |

| OUT5 17 O |     | 0   | Level shifter channel 5 output. Leave this pin floating, if not used.                                                                                                          |  |  |  |  |  |

| OUT6      | 18  | 0   | Level shifter channel 6 output. Leave this pin floating, if not used.                                                                                                          |  |  |  |  |  |

| OUT7      | 19  | 0   | Level shifter channel 7 output. Leave this pin floating, if not used.                                                                                                          |  |  |  |  |  |

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated

### **PIN FUNCTIONS (continued)**

| PIN                    |     | 1/0 | DESCRIPTION                                                                                         |  |  |  |  |  |

|------------------------|-----|-----|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME                   | NO. | 1/0 | DESCRIPTION                                                                                         |  |  |  |  |  |

| OUT8                   | 20  | 0   | Level shifter channel 8 output. Leave this pin floating, if not used.                               |  |  |  |  |  |

| OUT9                   | 21  | 0   | Level shifter channel 9 output. Leave this pin floating, if not used.                               |  |  |  |  |  |

| DISCHARGE              | 22  | 0   | Panel discharge output. Leave this pin floating, if not used.                                       |  |  |  |  |  |

| GND                    | 23  | Р   | Ground.                                                                                             |  |  |  |  |  |

| RE                     | 24  | 0   | Gate voltage shaping discharge resistor connection. Leave this pin floating, if not used.           |  |  |  |  |  |

| FLK3                   | 25  | I   | Gate voltage shaping flicker clock input for channels 3 and 6. Connect this pin to GND if not used. |  |  |  |  |  |

| FLK2                   | 26  | I   | Gate voltage shaping flicker clock input for channels 2 and 5. Connect this pin to GND if not used. |  |  |  |  |  |

| FLK1                   | 27  | I   | Gate voltage shaping flicker clock input for channels 1 and 4. Connect this pin to GND if not used. |  |  |  |  |  |

| VSENSE                 | 28  | I   | Panel discharge voltage sense. Connect this pin to GND, if not used.                                |  |  |  |  |  |

| Exposed<br>Thermal Die | Pad | Р   | Connect to VGL                                                                                      |  |  |  |  |  |

#### **TYPICAL CHARACTERISTICS**

#### **TABLE OF GRAPHS**

|                           |                                                                   | FIGURE    |

|---------------------------|-------------------------------------------------------------------|-----------|

| Output Rise and Fall Time | Channels 1 to 7, C <sub>L</sub> = 4.7 nF, rising edge             | Figure 1  |

|                           | Channels 1 to 7, C <sub>L</sub> = 4.7 nF, falling edge            | Figure 2  |

|                           | Channels 8 to 9, C <sub>L</sub> = 4.7 nF, rising edge             | Figure 3  |

|                           | Channels 8 to 9, C <sub>L</sub> = 4.7 nF, falling edge            | Figure 4  |

|                           | Channels 1 to 7, C <sub>L</sub> = 8 pF, rising edge               | Figure 5  |

|                           | Channels 1 to 7, C <sub>L</sub> = 8 pF, falling edge              | Figure 6  |

|                           | Channels 8 to 9, C <sub>L</sub> = 8 pF, rising edge               | Figure 7  |

|                           | Channels 8 to 9, C <sub>L</sub> = 8 pF, falling edge              | Figure 8  |

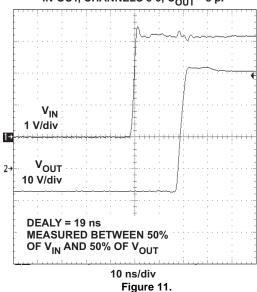

| Propagation Delay         | IN to OUT, channels 1 to 7, C <sub>L</sub> = 150 pF, rising edge  | Figure 9  |

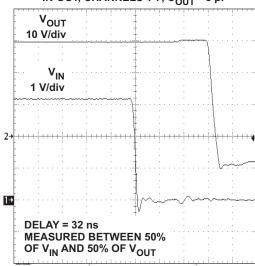

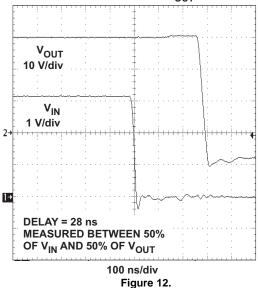

|                           | IN to OUT, channels 1 to 7, C <sub>L</sub> = 150 pF, falling edge | Figure 10 |

|                           | IN to OUT, channels 8 to 9, C <sub>L</sub> = 150 pF, rising edge  | Figure 11 |

|                           | IN to OUT, channels 8 to 9, C <sub>L</sub> = 150 pF, falling edge | Figure 12 |

|                           | FLK to OUT, channels 1 to 6, $C_L = 150$ pF, RE = 1 k $\Omega$    | Figure 13 |

| Output Current            | Channels 1 to 7, C <sub>L</sub> = 10 nF                           | Figure 14 |

|                           | Channels 8 to 9, C <sub>L</sub> = 10 nF                           | Figure 15 |

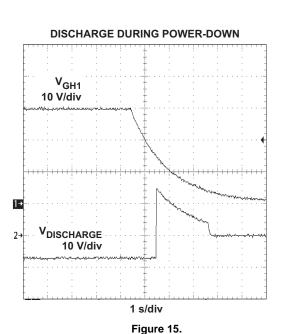

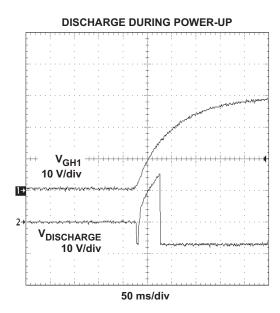

| Panel Discharge           | Power-on sequencing                                               | Figure 16 |

|                           | Power-off-sequencing                                              | Figure 17 |

Product Folder Link(s): TPS65192

200 ns/div Figure 1. OUTPUT RISE TIME CHANNELS 8-9, C<sub>OUT</sub>= 4.7 nF

Figure 3.

## OUTPUT FALL TIME CHANNELS 1-7, C<sub>OUT</sub> = 4.7 nF

200 ns/div

# Figure 2. OUTPUT FALL TIME CHANNELS 8-9, C<sub>OUT</sub> = 4.7 nF

Figure 5. OUTPUT RISE TIME CHANNELS 8-9, C<sub>OUT</sub> = 8 pF

#### OUTPUT FALL TIME CHANNELS 1-7, C<sub>OUT</sub> = 8 pF

Figure 6.

OUTPUT FALL TIME

CHANNELS 8-9, C<sub>OUT</sub> = 8 pF

5 ns/div Figure 9. PROPAGATION DELAY – RISING IN-OUT, CHANNELS 8-9, C<sub>OUT</sub> = 8 pF

## PROPAGATION DELAY – FALLING IN-OUT, CHANNELS 1-7, C<sub>OUT</sub> = 8 pF

10 ns/div Figure 10. PROPAGATION DELAY – FALLING IN-OUT, CHANNELS 8-9, C<sub>OUT</sub> = 8 pF

Figure 14.

#### **DETAILED DESCRIPTION**

#### **LEVEL SHIFTERS**

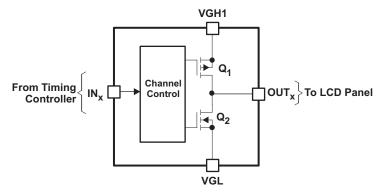

The 9 level shifter channels in the TPS65192 are divided into two groups. Channels 1 through 7 are powered from  $V_{GH1}$  and  $V_{GL}$ , channels 8 and 9 are powered from  $V_{GH2}$  and  $V_{GL}$ . Channels 1 to 6 support gate shaping and channels 7 through 9 do not (see the block diagram on page 1).

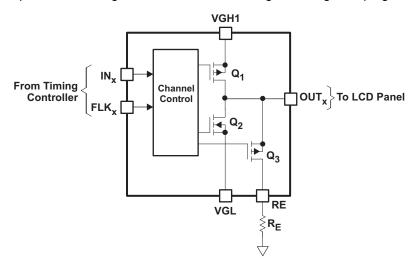

Figure 18 contains a simplified block diagram of one channel with gate voltage shaping.

Figure 18. Level Shifter Channel With Gate Voltage Shaping

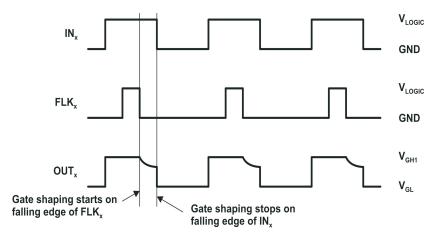

On the rising edge of IN,  $Q_1$  turns on,  $Q_2$  and  $Q_3$  turn off, and OUT is driven to  $V_{GH1}$ . On the falling edge of FLK,  $Q_1$  turns off,  $Q_3$  is turned on, and the panel now discharges through  $Q_3$  and RE (see Figure 19). On the falling edge of IN,  $Q_2$  turns on and  $Q_3$  turns off, and OUT is driven to  $V_{GL}$ . This sequence is repeated in turn for each channel.

10

Figure 19. Gate Voltage Shaping Timing Diagram

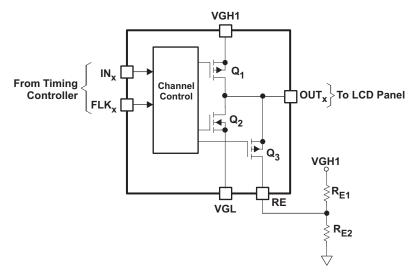

The alternative configuration shown in Figure 20 can be used to define a minimum gate voltage reached during gate voltage shaping.

Figure 20. Alternative Gate Voltage Shaping Circuit Configuration

In this circuit, resistors  $R_{E1}$  and  $R_{E2}$  define both the rate of change of gate voltage decay and the minimum gate voltage  $V_{MIN}$ . Using the Thevenin equivalent, the operating parameters of Figure 20 are easily expressed as follows:

$$V_{MIN} = V_{VGH1} \times \left(\frac{R_{E2}}{R_{E1} + R_{E2}}\right)$$

$$R_{E} = \frac{R_{E1} \times R_{E2}}{R_{E1} + R_{E2}}$$

(1)

#### **FLICKER CLOCKS**

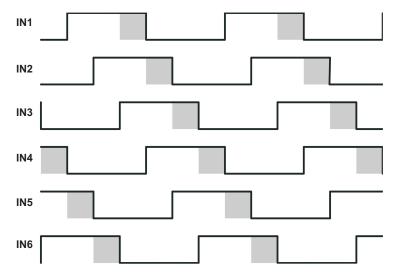

The gate voltage shaping control logic in the TPS65192 allows the device to be used with one, two or three flicker clock signals, according to the application requirements.

In 6-phase applications where one signal controls gate voltage shaping for six CLK channels, the flicker clock should be connected to FLK1 and the unused pins FLK2 and FLK3 connected to GND.

Copyright © 2009, Texas Instruments Incorporated

TEXAS INSTRUMENTS

SLVS962-JULY 2009 www.ti.com

In 6-phase applications where three signals control gate voltage shaping for six CLK channels, the flicker clock for channels 1 and 4 should be connected to FLK1, the flicker clock for channels 2 and 5 connected to FLK2, and the flicker clock for channels 3 and 6 connected to FLK3.

In 4-phase applications where two signals control gate voltage shaping for four CLK channels, the flicker clock for phases 1 and 3 should be connected to FLK1, the flicker clock for phases 2 and 4 connected to FLK2, and the unused pin FLK3 connected to GND. The unused pins IN 3 and IN6 should be connected to  $V_{LOGIC}$ . Alternatively, IN3 can be connected to IN2 and IN6 connected to IN5; this arrangement can simplify PCB layout. Typical schematics for each of the above cases are included in the *Applications* section of this data sheet.

Gate voltage shaping is started by the falling edge of the FLK signal(s), which must occur during a valid part of the clock waveform. For 6-phase systems, this means the last 60° of the clock waveform; for 4-phase systems, this means the last 90° of the clock waveform (see Figure 21 and Figure 22). Falling edges of the FLK signal(s) occurring outside the valid part of the clock waveform are ignored. The rising edge of the FLK signal(s) has no effect, regardless of when it occurs.

Note that gate voltage shaping is disabled when the voltage applied to the VSENSE pin is less than V<sub>REF</sub>.

Figure 21. FLK Falling Edge Validity, 6-Phase Applications

Figure 22. FLK Falling Edge Validity, 4-Phase Applications

12

#### LEVEL SHIFTERS WITHOUT GATE VOLTAGE SHAPING

Channels 7 through 9 do not support gate voltage shaping and are controlled only by the logic level applied to their  $IN_x$  pin. Figure 23 contains a block diagram of a channel that does not support gate voltage shaping.

Figure 23. Block Diagram of Level Shifter Without Gate Voltage Shaping

#### **PANEL DISCHARGE**

The TPS65192 contains a function for discharging the display panel during power-down. The discharge function comprises a comparator and a level shifter (see Figure 24). During normal operation, the voltage applied to the VSENSE pin is greater than  $V_{REF}$ , the output of the level shifter is low, and the DISCHARGE signal is at  $V_{GL}$ . During power-down, when the voltage applied to the VSENSE pin falls below  $V_{REF}$ , the level shifter output goes high and the DISCHARGE signal tracks  $V_{GH1}$  as it discharges (see Figure 16 and Figure 17). Note that gate voltage shaping is disabled when the voltage applied to the VSENSE pin is less than  $V_{REF}$ .

Figure 24. Panel Discharge Function Block Diagram

Suitable values for resistors R1 and R2 in Figure 24 can be calculated as follows:

$$R_1 = R_2 \times \left(\frac{V_X}{V_{REF}} - 1\right) = R_2 \times \left(\frac{V_X}{1.5 \text{ V}} - 1\right)$$

(2)

Where  $V_x$  is the voltage used to activate/deactivate the discharge function.

For most applications, a value between  $1k\Omega$  and  $10k\Omega$  for  $R_2$  can be used ( $R_1$  depends on the value of  $R_2$  and the value of  $V_x$ ).

Copyright © 2009, Texas Instruments Incorporated

#### APPLICATION INFORMATION

#### **Power Supply Decoupling**

For proper performance, it is recommended that each power supply rail be decoupled with high quality ceramic decoupling capacitors placed as close to the IC supply pins as possible. The exact values used should be optimized for each application, but a parallel combination of 10µF and 100nF is a good place to start.

#### **PCB LAYOUT**

The output stages of the TPS65192 are capable of sinking and sourcing high peak currents – greater than 500mA in typical applications – and care must be taken during PCB layout to ensure that this performance can be achieved in practice. In particular, the high rates of change of current occurring at the rising and falling edges of each output require stray inductance to be minimized. This is most easily achieved by routing the output signals using short, wide PCB tracks (as far as this is possible) and using a low impedance ground plane on the other side of the board to conduct return currents. Tracks between the decoupling capacitors and the corresponding power supply pins should also be kept short and wide as possible.

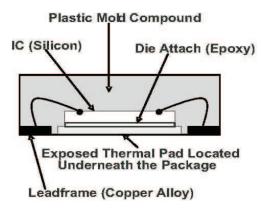

PCB layout must also be adequate from a thermal as well as electrical point of view. The TPS65192 is supplied in a 28-pin QFN package designed to eliminate the need for heat sinks to dissipate the power generated in the IC. The package, shown in Figure 25, is designed so that the lead-frame die pad is exposed on the bottom of the IC, thereby providing an extremely low thermal resistance path between the die and the exterior of the package  $(R_{\theta JC})$ .

Figure 25. Section View of a QFN Package

Copper areas in and on a PCB act as heat sinks for the QFN device; however, signal routing typically restricts access to the power pad on the top layer of the PCB. In typical applications, therefore, the main copper area used to conduct heat away from the IC is on the bottom layer.

TI recommends placing thermal vias in the solder mask defined thermal pad to transfer heat from the top layer of the PCB to the inner or bottom layer used for heat sinking. The recommended via diameter is 0.3mm or less, and via spacing 1mm (see Figure 26). For the  $5 \times 5$  mm QFN package used for the TPS65192, five thermal vias are typically used.

Submit Documentation Feedback

Figure 26. Recommended Thermal Via Spacing

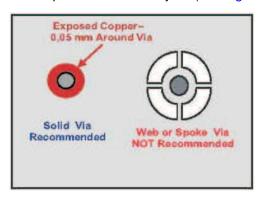

The thermal vias should make their connection to the bottom (or internal) copper plane with a complete connection around the entire circumference of the plated through hole, and a ring of exposed copper (0.05mm wide) around the vias at the bottom of the copper plane. It is not recommended to cover the vias with solder mask as this can cause excessive voiding, and nor is it recommended to use a thermal relief web or spoke connection as this impedes the conduction path to the other layers (see Figure 27).

Figure 27. Thermal Via Connection at the Bottom Layer

In any design, the copper areas used as heat sinks should be made as large as possible.

The power pad of the TPS65192 is electrically connected to VGL and therefore must not be connected to the PCB's ground plane.

For more detailed information concerning the thermal performance of QFN packages and recommendations about how to mount the ICs on a PCB, refer to the following application reports:

SLOA122 QFN Layout Guidelines SLUA271A QFN/SON PCB Attachment

## TEXAS INSTRUMENTS

#### **APPLICATION CIRCUITS**

Figure 28. Typical 6-Phase HD TV Application with One Flicker Clock

Figure 29. Typical 6-Phase F-HD TV Application with Three Flicker Clocks

Figure 30. Typical 4-Phase Monitor Application with Two Flicker Clocks

#### PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TPS65192RHDR     | ACTIVE | VQFN         | RHD                | 28   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>65192            | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

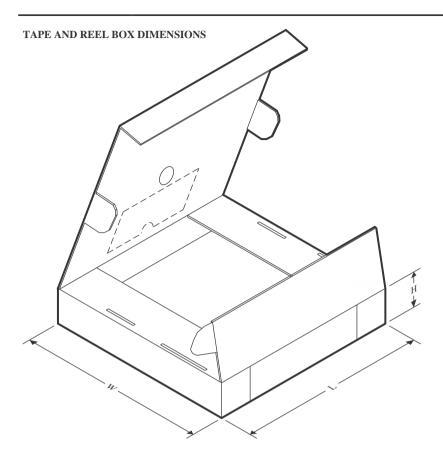

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 4-May-2023

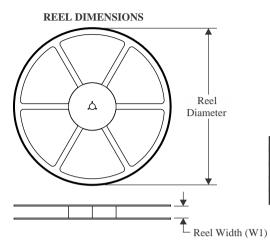

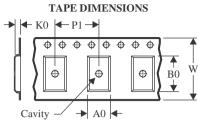

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

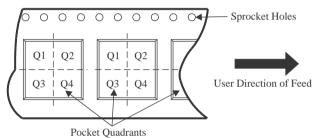

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS65192RHDR | VQFN            | RHD                | 28 | 3000 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.1        | 8.0        | 12.0      | Q2               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 4-May-2023

#### \*All dimensions are nominal

|   | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ١ | TPS65192RHDR | VQFN         | RHD             | 28   | 3000 | 346.0       | 346.0      | 33.0        |  |

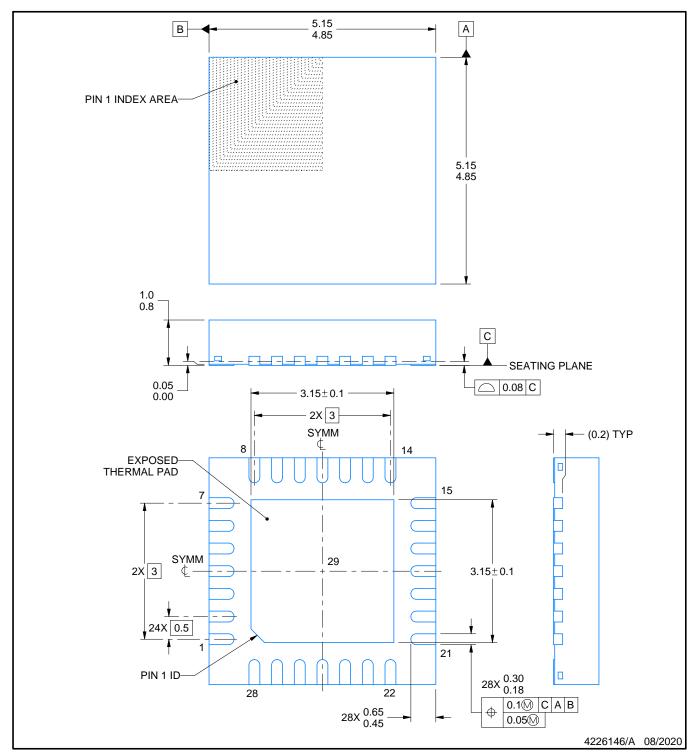

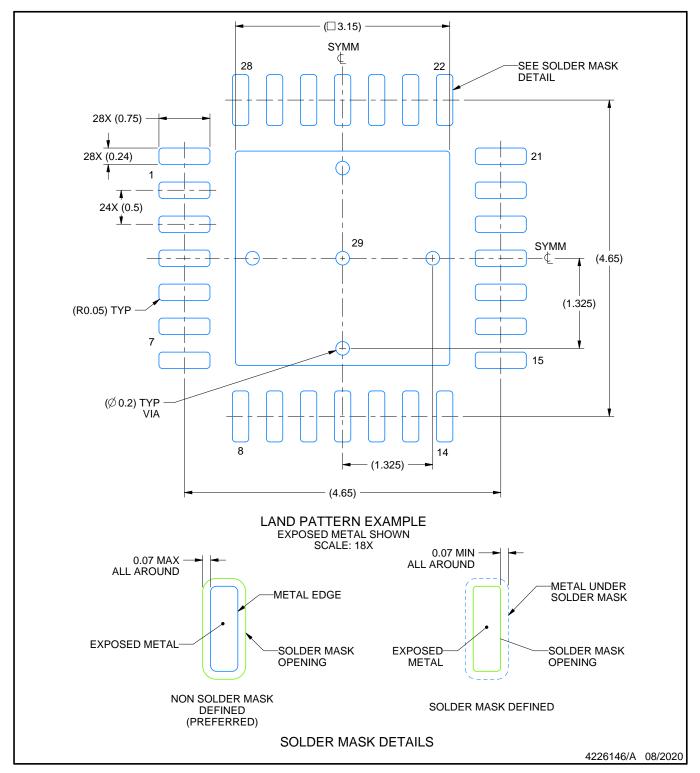

5 x 5 mm, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

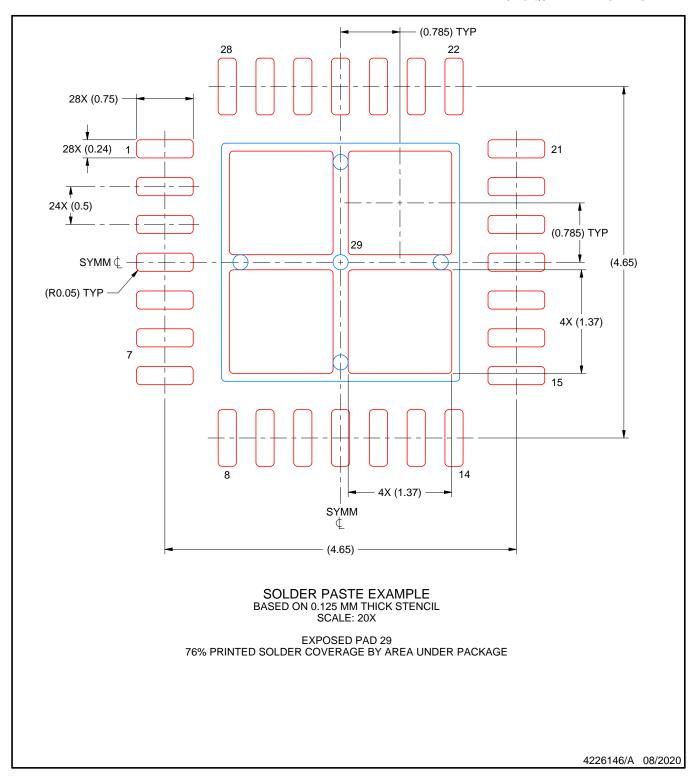

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

<sup>6.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated