# Winbond ExpressCard™ Power Interface Switch W83L351 Series

# <u>W83L351 Series</u> Data Sheet Revision History

| NO | PAGES | DATES        | VERSION | VERSION<br>ON WEB | MAIN CONTENTS                                            |

|----|-------|--------------|---------|-------------------|----------------------------------------------------------|

| 1. | All   | Apr. /07     | 1.0     | N.A               | All versions before 1.0 are preliminary versions.        |

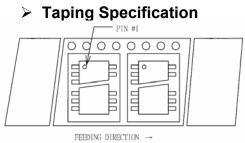

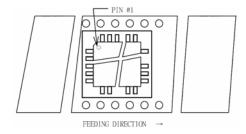

| 2  | 28    | July 5, 2007 | 1.1     |                   | Update the ordering information and add the taping spec. |

| 3  |       |              |         |                   |                                                          |

| 4  |       |              |         |                   |                                                          |

| 5  |       |              |         |                   |                                                          |

| 6  |       |              |         |                   |                                                          |

| 7  |       |              |         |                   |                                                          |

|    |       |              |         |                   |                                                          |

# Table of Contents-

| 1.  | FEATURES                          | 1  |

|-----|-----------------------------------|----|

| 2.  | PIN CONFIGURATION AND DESCRIPTION | 2  |

| 3.  | APPLICATION CIRCUIT               | 5  |

| 4.  | INTERNAL BLOCK DIAGRAM            | 6  |

| 5.  | ABSOLUTE MAXIMUM RATINGS          | 7  |

| 6.  | RECOMMENDED OPERATING CONDITIONS  | 8  |

| 7.  | ELECTRICAL CHARACTERISTICS        | 9  |

| 8.  | SWITCHING CHARACTERISTICS         | 12 |

| 9.  | FUNCTIONAL TRUTH TABLES           | 13 |

| 10. | TYPICAL OPERATING WAVEFORMS       | 15 |

| 11. | EXPRESSCARD TIMING DIAGRAMS       | 20 |

| 12. | PACKAGE DIMENSION                 | 24 |

| 13. | ORDERING INFORMATION              | 28 |

| 14. | TOP MARKING SPECIFICATION         | 29 |

### 1. FEATURES

- Meets the ExpressCard™ Standard (ExpressCard|34 or ExpressCard|54)

- Compliant with the ExpressCard™ Compliance Checklists

- ExpressCard Compliance ID: EC100098 (W83L351G), EC100115 (W83L351YG/YCG)

- Fully Satisfies the ExpressCard™ Implementation Guidelines

- Supports System with WAKE Function

- TTL-Logic Compatible Inputs

- Short Circuit and Thermal Protection

- 0°C to 70°C Ambient Operating Temperature Range

- Available in a 20-pin TSSOP or a 20-pin QFN

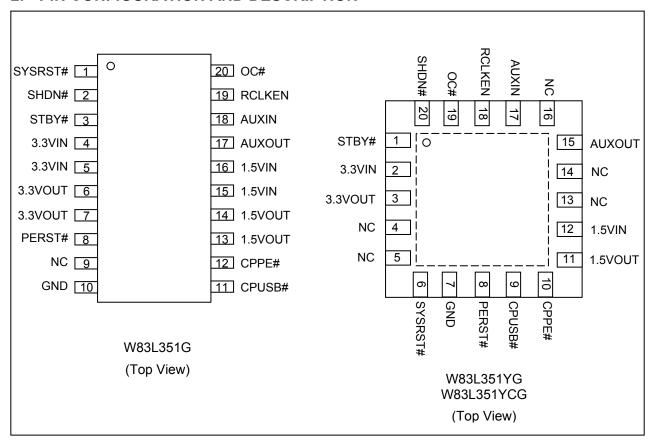

### 2. PIN CONFIGURATION AND DESCRIPTION

|         | Р | IN  |                  |                                                                                                                                                                                                                                                                     |  |  |  |

|---------|---|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYMBOL  | G | YG  | I/O              | FUNCTION                                                                                                                                                                                                                                                            |  |  |  |

|         | G | YCG |                  |                                                                                                                                                                                                                                                                     |  |  |  |

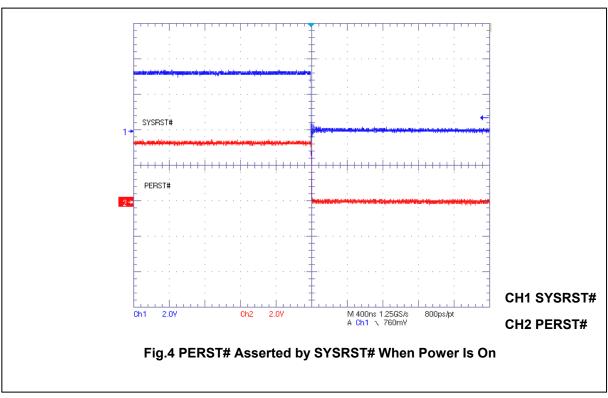

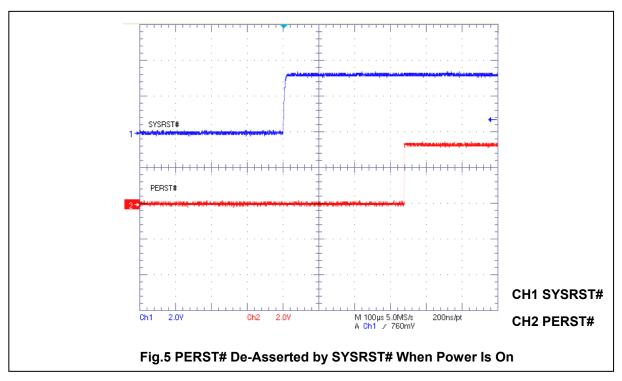

| SYSRST# | 1 | 6   | l <sup>(*)</sup> | System Reset input – active low, logic level signal. Internally pulled up to AUXIN. This input is driven by the host system and directly affects PERST#. Asserting SYSRST# (logic low) forces PERST# to assert. RCLKEN is not affected by the assertion of SYSRST#. |  |  |  |

| SHDN#   | 2 | 20  | l <sup>(*)</sup> | Shutdown input – active low, logic level signal. Internally pulled up to AUXIN. When asserted (logic low), this input instructs the power switch to turn off all voltage outputs and the discharge FETs are activated.                                              |  |  |  |

### Continued

|        | Р  | IN        |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|----|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL | G  | YG<br>YCG | I/O              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| STBY#  | 3  | 1         | l <sup>(*)</sup> | Standby input – active low, logic level signal. Internally pulled up to AUXIN. When asserted (logic low) after the card is inserted, this input places the power switch in standby mode by turning off the 3.3V and 1.5V power switches and keeping the AUX switch on. If the signal is asserted prior to the card being present, STBY# places the power switch in OFF Mode by turning off the AUX, 3.3V, and 1.5V power switches.                      |

|        |    |           |                  | A logic level power good (with delay). When powered up, this output remains asserted (logic level low) until all power rails are within the tolerance. Once all power rails are within the tolerance and RCLKEN has been released (logic high), PERST# is deasserted (logic high) after a time delay, as shown in the parametric table. When powered down, this output is asserted whenever any of the power rails drops below their voltage tolerance. |

|        |    |           |                  | The PERST# signal is an output from the host system and an input to the ExpressCard module. This signal is only used by PCI Express-based modules and its function is to place the ExpressCard module in a reset state.                                                                                                                                                                                                                                 |

| PERST# | 8  | 8         | 0                | During power up, power down, or whenever power to the ExpressCard module is not stable or not within voltage tolerance limits, the ExpressCard standard requires that PERST# be asserted. As a result, this signal also serves as a power-good indicator to the ExpressCard module, and the relationship between the power rails and PERST# are explicitly defined in the ExpressCard standard.                                                         |

|        |    |           |                  | The host can also place the ExpressCard module in a reset state by asserting a system reset SYSRST#. This system reset generates a PERST# signal to the ExpressCard module without disrupting the voltage rails. This is normally called a warm reset. However, in a cold start situation, the system reset can also be used to prolong the assertion time of PERST#.                                                                                   |

| CPUSB# | 11 | 9         | l <sup>(*)</sup> | Card Present input for USB cards. Internally pulled up to AUXIN. A logic low level on this input indicates that the card present supports the USB functions. When a card is inserted, CPUSB# is physically connected to ground if the card supports USB functions.                                                                                                                                                                                      |

| CPPE#  | 12 | 10        | l <sup>(*)</sup> | Card Present input for PCI Express cards. Internally pulled up to AUXIN. A logic low level on this input indicates that the card present supports the PCI Express functions. When a card is inserted, CPPE# is physically connected to ground if the card supports PCI Express functions.                                                                                                                                                               |

### Continued

| PIN     |           | N                         |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-----------|---------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL  |           | YG                        | I/O                 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | G         | YCG                       |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RCLKEN  | 19        | 18                        | I <sup>(*)</sup> /O | Reference Clock Enable signal. As an output, it is a logic level power good to the host (no delay – open drain). As an input, if the signal is kept inactive (low) by the host, PERST# will be prevented from being de-asserted. Internally pulled up to AUXIN. This pin serves both as an input and an output. When powered up, a discharge FET keeps this signal at a low state as long as any of the output power rails is out of their tolerance range. Once all output power rails are within the tolerance, the switch releases RCLKEN, allowing it to transit to a high state (internally pulled up to AUXIN). |

|         |           |                           |                     | The transition of RCLKEN from a low to a high state starts an internal timer for the purpose of de-asserting PERST#. As an input, RCLKEN can be kept low to delay the start of the PERST# internal timer. Because RCLKEN is internally connected to a discharge FET, this pin can only be driven low and should never be driven high as a logic input. When an external circuit drives this pin low, RCLKEN becomes an input; otherwise, this pin is an output.                                                                                                                                                       |

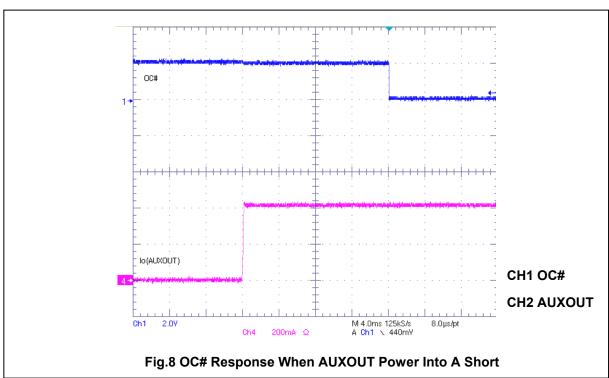

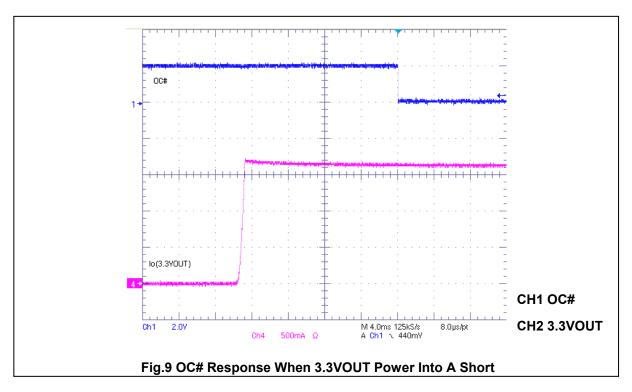

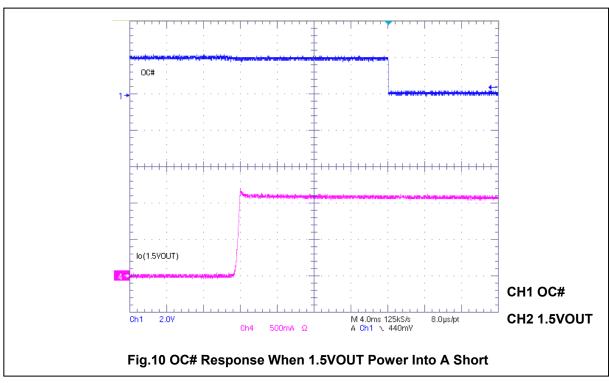

| OC#     | 20        | 19                        | OD                  | Over current status output (open drain). This pin is an open-drain output. When any of the three power switches (AUX, 3.3V, and 1.5V) is in an over current condition, OC# is asserted (logic low) by an internal discharge FET with a deglitch delay. Otherwise, the discharge FET is open, and the pin can be pulled up to a power supply through an external resistor.                                                                                                                                                                                                                                             |

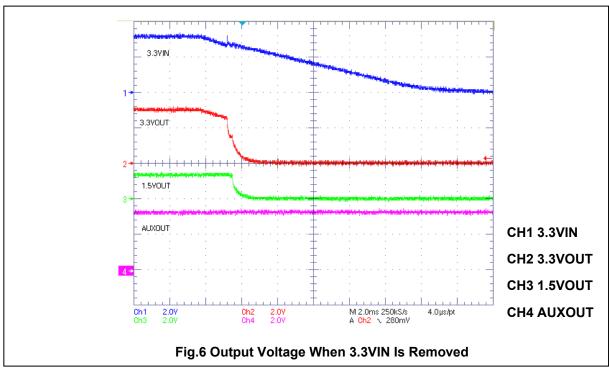

| 3.3VIN  | 4, 5      | 2                         | I                   | Primary voltage source, 3.3V input for 3.3VOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

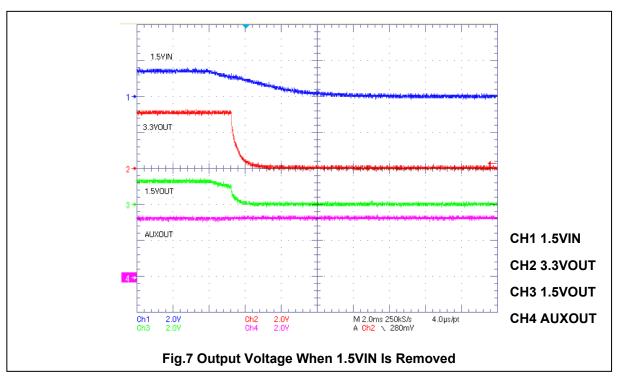

| 1.5VIN  | 15,16     | 12                        | ı                   | Secondary voltage source, 1.5V input for 1.5VOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AUXIN   | 18        | 17                        | I                   | Auxiliary voltage source, AUX input for AUXOUT and chip power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3VOUT | 6, 7      | 3                         | 0                   | Switched output that delivers 0V, 3.3V or high impedance to the card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.5VOUT | 13,<br>14 | 11                        | 0                   | Switched output that delivers 0V, 1.5V or high impedance to the card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AUXOUT  | 17        | 15                        | 0                   | Switched output that delivers 0V, AUX or high impedance to the card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GND     | 10        | 7                         |                     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NC      | 9         | 4, 5,<br>13,<br>14,<br>16 |                     | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

**Notice:** (\*) Be aware that no input pins can be driven HIGH before the Auxiliary voltage is VALID.

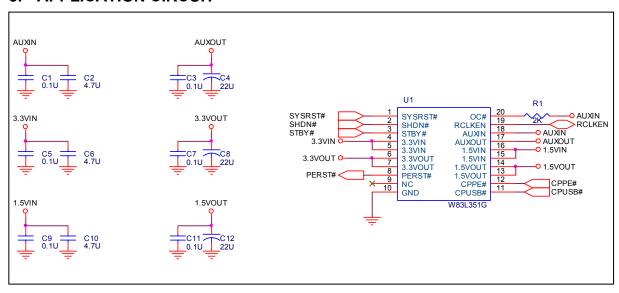

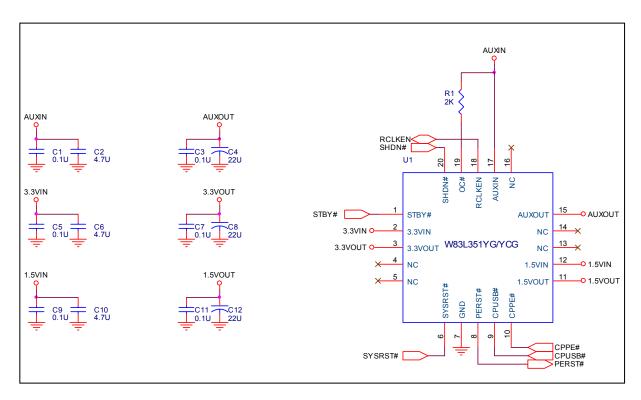

### 3. APPLICATION CIRCUIT

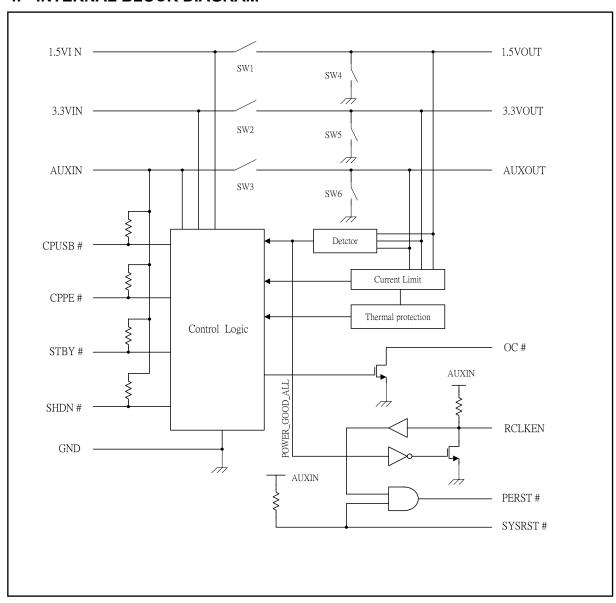

### 4. INTERNAL BLOCK DIAGRAM

### 5. ABSOLUTE MAXIMUM RATINGS

| ITEM                               | SYMBOL                  | RATING             | UNIT    |  |

|------------------------------------|-------------------------|--------------------|---------|--|

|                                    | V <sub>I(3.3VIN)</sub>  | -0.3 to 6          | V       |  |

| Input Voltage                      | V <sub>I(1.5VIN)</sub>  | -0.3 to 6          | V       |  |

|                                    | $V_{I(AUXIN)}$          | -0.3 to 6          | V       |  |

| Logic Input/Output Voltage         | -0.3 to 6               | V                  |         |  |

|                                    | V <sub>O(3.3VOUT)</sub> | -0.3 to 6          | V       |  |

| Output Voltage                     | V <sub>O(1.5VOUT)</sub> | -0.3 to 6          | V       |  |

|                                    | $V_{O(AUXOUT)}$         | -0.3 to 6          | V       |  |

|                                    | I <sub>O(3.3OUT)</sub>  | Internally limited |         |  |

| Output Current                     | I <sub>O(1.5OUT)</sub>  | Internally limited |         |  |

|                                    | I <sub>O(AUXOUT)</sub>  | Internally         | limited |  |

| Operating Temperature Range        | $T_{opt}$               | 0 to 70            | °C      |  |

|                                    | Human Body Mode         | ±2                 | kV      |  |

| Electrostatic discharge protection | Machine Mode            | ±200               | V       |  |

|                                    | Latch-Up                | ±100               | mA      |  |

# 6. RECOMMENDED OPERATING CONDITIONS

| ITEM                         |                         |                                                      | MIN  | MAX  | UNIT |

|------------------------------|-------------------------|------------------------------------------------------|------|------|------|

|                              | V <sub>I(3.3VIN)</sub>  | 3.3VIN is only required for its respective functions | 3    | 3.6  |      |

| Input Voltage                | V <sub>I(1.5VIN)</sub>  | 1.5VIN is only required for its respective functions | 1.35 | 1.65 | V    |

|                              | $V_{I(AUXIN)}$          | AUXIN is required for all circuit operations         | 3    | 3.6  |      |

|                              | I <sub>O(3.3VOUT)</sub> |                                                      | 0    | 1.3  | Α    |

| Continuous output<br>current | I <sub>O(1.5VOUT)</sub> | TJ=120°C                                             | 0    | 650  | mA   |

|                              | I <sub>O(AUXOUT)</sub>  |                                                      | 0    | 275  | mA   |

### 7. ELECTRICAL CHARACTERISTICS

$T_A = 25^{\circ}\text{C}$ ,  $V_{\text{I (3.3VIN)}} = V_{\text{I (AUXIN)}} = 3.3 \text{ V}$ ,  $V_{\text{I (1.5VIN)}} = 1.5 \text{ V}$ ,  $V_{\text{I (SHDN#)}}$ ,  $V_{\text{I (STBY#)}} = 3.3 \text{ V}$ ,  $V_{\text{I (CPPE#)}} = V_{\text{I (CPUSB#)}} = 0 \text{ V}$ ,  $V_{\text{I (SYSRST)}} = 3.3 \text{ V}$ , OC# and RCLKEN and PERST# are open, all voltage outputs unloaded (unless otherwise noted)

|                                            | PARAMETER                           |                        | TEST CONDITIONS                                                    | MIN      | TYP      | MAX | UNIT |  |

|--------------------------------------------|-------------------------------------|------------------------|--------------------------------------------------------------------|----------|----------|-----|------|--|

|                                            | 3.3VIN to 3.3VOUT with              |                        | TA = 25°C, $I = 1305$ mA each                                      |          | 90       |     |      |  |

| Power<br>switch<br>resistance              | two switches                        | on for dual            | TA = 70°C, I = 1305 mA each                                        |          |          | 105 |      |  |

|                                            | 1.5VIN to 1.5                       |                        | TA = 25°C, I = 660 mA each                                         |          | 90       |     | mΩ   |  |

|                                            | two switches                        | on for dual            | TA = 70°C, I = 660 mA each                                         |          |          | 110 |      |  |

|                                            | AUXIN to AU                         |                        | TA = 25°C, I = 285 mA each                                         |          | 110      |     |      |  |

|                                            | two switches                        | on for dual            | TA = 70°C, I = 285 mA each                                         |          |          | 126 |      |  |

| I <sub>OS</sub><br>Short –                 | I <sub>OS(3.3VOUT)</sub> (st value) | eady-state             |                                                                    | 1.3<br>5 | 1.7      | 2.5 | Α    |  |

| circuit<br>output                          | I <sub>OS(1.5VOUT)</sub> (st value) | eady-state             | Output powered into a short                                        | 0.6<br>7 | 1.1      | 1.3 | Α    |  |

| current                                    | I <sub>OS(AUXOUT)</sub> (stevalue)  | eady-state             |                                                                    | 275      | 400      | 600 | mA   |  |

| Thermal                                    | Trip point, T <sub>J</sub>          |                        | Rising temperature, not in over current condition                  |          | 155      |     | 90   |  |

| Shutdown                                   |                                     |                        | Over current condition                                             |          | 130      |     | °C   |  |

|                                            | Hysteresis                          |                        |                                                                    |          | 10       |     |      |  |

|                                            | Normal operation                    | $I_{I(AUXIN)}$         | Outputs are unloaded                                               |          | 140      | 210 |      |  |

|                                            |                                     | I <sub>I(3.3VIN)</sub> | (include CPPE# and CPUSB# logic pull-up                            |          | 10.<br>5 | 15  | uA   |  |

|                                            |                                     | I <sub>I(1.5VIN)</sub> | currents)                                                          |          | 2.2      | 10  | 1    |  |

|                                            |                                     | I <sub>I(AUXIN)</sub>  | CPUSB# = CPPE# = 0 V                                               |          | 170      | 270 |      |  |

|                                            | Shutdown                            | I <sub>I(3.3VIN)</sub> | SHDN# = 0 V (discharge<br>FETs are on) (include                    |          | 6        | 10  |      |  |

| I <sub>I</sub><br>Total input<br>quiescent | mode                                | I <sub>I(1.5VIN)</sub> | CPPE# and CPUSB# logic pull-up currents and SHDN# pull-up current) |          | 2.2      | 10  | uA   |  |

| current<br>(Note: 1)                       |                                     | I <sub>I(AUXIN)</sub>  | CPUSB# = CPPE# = 0 V                                               |          | 170      | 270 |      |  |

| (Note. 1)                                  | Standby                             | I <sub>I(3.3VIN)</sub> | STBY# = 0 V (include<br>CPPE# and CPUSB# logic                     |          | 6        | 10  | uA   |  |

|                                            | mode (1)                            | I <sub>I(1.5VIN)</sub> | pull-up currents and STBY#<br>pull-up current)                     |          | 2.2      | 10  | u/\  |  |

|                                            | _                                   | I <sub>I(AUXIN)</sub>  | CPUSB# = CPPE# = 0 V                                               |          | 160      | 210 |      |  |

|                                            | Standby<br>mode (2)                 | I <sub>I(3.3VIN)</sub> | 3.3VIN = 0 V (include<br>CPPE# and CPUSB# logic                    |          | 0        | 0.1 | uA   |  |

|                                            | (-)                                 | I <sub>I(1.5VIN)</sub> | pull-up currents)                                                  |          | 2.2      | 10  |      |  |

### Continued

|                                                                     | PARAMETER                |                        | TEST CONDITIONS                                                      | MIN   | TYP                               | MAX   | UNIT |  |

|---------------------------------------------------------------------|--------------------------|------------------------|----------------------------------------------------------------------|-------|-----------------------------------|-------|------|--|

|                                                                     | 04 "                     | I <sub>I(AUXIN)</sub>  | CPUSB# = CPPE# = 0 V                                                 |       | 160                               | 210   |      |  |

|                                                                     | Standby<br>mode (3)      | I <sub>I(3.3VIN)</sub> | 1.5VIN = 0 V (include<br>CPPE# and CPUSB# logic                      |       | 6                                 | 10    | uA   |  |

|                                                                     |                          | I <sub>I(1.5VIN)</sub> | pull-up currents)                                                    |       | 0                                 | 0.1   |      |  |

| lu (EMP)                                                            | I <sub>I(AU</sub>        | XIN)                   | SHDN# = 3.3 V, CPUSB# =                                              |       | 22                                | 50    |      |  |

| I <sub>lkg(FWD)</sub><br>Forward                                    | I <sub>I(3.3</sub>       | VIN)                   | CPPE# = 3.3 V (no card present, discharge FETs are                   |       | 0                                 | 50    | uA   |  |

| leakage<br>current                                                  | I <sub>I(1.5</sub>       | VIN)                   | on);current measured at input pins, includes RCLKEN pull- up current |       | 0                                 | 50    | uA   |  |

| LOGIC SECT                                                          | ION (SYSRS)              | r, shdn#, st           | BY#, PERST#, RCLKEN , OC#                                            | , CPU | SB#, C                            | PPE#) |      |  |

|                                                                     |                          |                        | SYSRST# = 3.6 V, sinking                                             |       | 0                                 |       |      |  |

|                                                                     | I <sub>(SYSRS#)</sub>    | Input                  | SYSRST# = 0 V, sourcing                                              | 10    | 17.<br>5                          | 30    | uA   |  |

|                                                                     |                          |                        | SHDN# = 3.6 V, sinking                                               |       | 0                                 |       |      |  |

|                                                                     | I <sub>(SHDN#)</sub>     | Input                  | SHDN# = 0 V, sourcing                                                | 10    | 17.<br>5                          | 30    | uA   |  |

| Logic input supply                                                  | I <sub>(STBY#)</sub>     |                        | STBY# = 3.6 V, sinking                                               |       | 0                                 |       |      |  |

| current                                                             |                          | Input                  | STBY# = 0 V, sourcing                                                | 10    | 17.<br>5                          | 30    | uA   |  |

|                                                                     | I <sub>(RCLKEN)</sub>    | Input                  | RCLKEN = 0 V, sourcing                                               | 10    | 18                                | 30    | uA   |  |

|                                                                     | I <sub>(CPUSB#)</sub> or | innute                 | CPUSB# or CPPE# = 0 V, sinking                                       |       | 0                                 |       | uA   |  |

|                                                                     | I <sub>(CPPE#)</sub>     | inputs                 | CPUSB# or CPPE# = 3.6 V, sourcing                                    | 10    | 17.<br>5                          | 30    | uA   |  |

| Logic input                                                         | High                     | level                  |                                                                      | 2     | 10 18 30<br>0 0<br>10 17.<br>5 30 |       | V    |  |

| voltage                                                             | Low                      | level                  |                                                                      |       |                                   | 0.8   | V    |  |

| RCLKEN ou voltage                                                   | tput low                 | Output                 | IO(RCLKEN) = 60 μA                                                   |       |                                   | 0.4   | V    |  |

|                                                                     | sertion thresho          |                        | 3.3VOUT falling                                                      | 2.7   |                                   | 3     |      |  |

| voltage (PERST# asserted when any<br>output voltage falls below the |                          | AUXOUT falling         | 2.7                                                                  |       | 3                                 | V     |      |  |

| threshold)                                                          | go rano porori           |                        | 1.5VOUT falling                                                      | 1.2   | 1.2                               |       |      |  |

| PERST# as voltage                                                   | sertion delay            | from output            | 3.3VOUT, AUXOUT,<br>1.5VOUT falling                                  |       |                                   | 500   | ns   |  |

| PERST# c                                                            |                          | delay from             | 3.3VOUT, AUXOUT, or<br>1.5VOUT rising within<br>tolerance            | 1     | 20                                |       | ms   |  |

### Continued

| PARAMETER                                         | TEST CONDITIONS                                                                       | MIN | TYP | MAX  | UNIT |

|---------------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|------|------|

| PERST# assertion delay from SYSRST#               | Max time from SYSRST asserted                                                         |     | 25  | 500  | ns   |

| t <sub>W(PERST#)</sub> PERST# minimum pulse width | 3.3VOUT, AUXOUT, or<br>1.5VOUT falling out of<br>tolerance or triggered by<br>SYSRST# | 100 | 340 |      | us   |

| PERST# output low voltage                         | - 500 uA                                                                              |     |     | 0.4  | V    |

| PERST# output high voltage                        | I <sub>O(PERST#)</sub> = 500 μA                                                       | 2.4 |     |      | V    |

| OC# output low voltage                            | I <sub>O(OC#)</sub> = 2 mA                                                            |     |     | 0.4  | V    |

| OC# deglitch                                      | Falling into or out of an over current condition                                      |     | 20  |      | ms   |

| UNDERVOLTAGE LOCKOUT (UVLO)                       |                                                                                       |     |     |      |      |

| 3.3VIN UVLO                                       | 3.3VIN level, below which 3.3VIN and 1.5VIN switches are off                          | 2.6 |     | 2.9  |      |

| 1.5VIN UVLO                                       | 1.5VIN level, below which 3.3VIN and 1.5VIN switches are off                          | 1.0 |     | 1.25 | V    |

| AUXIN UVLO                                        | AUXIN level, below which all switches are off                                         | 2.6 |     | 2.9  |      |

| UVLO hysteresis                                   |                                                                                       |     | 100 |      | mV   |

Note 1: In the Shutdown mode or the Standby mode (1), the AUXIN quiescent current includes a normal operation current, SHDN# or STBY# internal pull-up current and RCLKEN internal pull-up current. In the Standby modes (2) & (3), the AUXIN quiescent current includes a normal operation current and a RCLKEN internal-up current.

### 8. SWITCHING CHARACTERISTICS

$T_A = 25^{\circ}\text{C}$ ,  $V_{\text{I (3.3VIN)}} = V_{\text{I (AUXIN)}} = 3.3 \text{ V}$ ,  $V_{\text{I (1.5VIN)}} = 1.5 \text{ V}$ ,  $V_{\text{I (SHDN#)}}$ ,  $V_{\text{I (STBY#)}} = 3.3 \text{ V}$ ,  $V_{\text{I (CPPE#)}} = V_{\text{I (CPUSB#)}} = 0 \text{ V}$ ,  $V_{\text{I (SYSRST)}} = 3.3 \text{ V}$ , OC# and RCLKEN and PERST# are open, all voltage outputs unloaded (unless otherwise noted)

| DADAI                               | WETED             | TEST COMPLIANCE                                                                    | MINI | TVD | MAY | LINUT |  |

|-------------------------------------|-------------------|------------------------------------------------------------------------------------|------|-----|-----|-------|--|

| PARAI                               | METER             | TEST CONDITIONS                                                                    | MIN  | TYP | MAX | UNIT  |  |

| t <sub>r</sub>                      | 3.3VIN to 3.3VOUT | $C_{L(3.3VOUT)}=0.1uF, I_{O(3.3VOUT)}=0A$                                          | 0.1  |     | 6   |       |  |

|                                     | AUXIN to AUXOUT   | $C_{L(AUXVOUT)}=0.1uF, I_{O(AUXOUT)}=0A$                                           | 0.1  |     | 6   |       |  |

|                                     | 1.5VIN to 1.5VOUT | C <sub>L(1.5VOUT)</sub> =0.1uF, I <sub>O(1.5VOUT)</sub> =0A                        | 0.1  |     | 6   |       |  |

|                                     | 3.3VIN to 3.3VOUT | C <sub>L(3.3VOUT)</sub> =100uF, R <sub>L</sub> =V <sub>I(3.3VIN)</sub> /1A         | 0.1  |     | 6   | ms    |  |

| Output rise times                   | AUXIN to AUXOUT   | C <sub>L(AUXVOUT)</sub> =100uF,<br>R <sub>L</sub> =V <sub>I(AUXININ)</sub> /0.250A | 0.1  |     | 6   |       |  |

|                                     | 1.5VIN to 1.5VOUT | C <sub>L(1.5VOUT)</sub> =100uF,<br>R <sub>L</sub> =V <sub>I(1.5VIN)</sub> /0.500A  | 0.1  |     | 6   |       |  |

| t <sub>f</sub>                      | 3.3VIN to 3.3VOUT | $C_{L(3.3VOUT)} = 0.1 uF, I_{O(3.3VOUT)} = 0A$                                     | 10   |     | 150 |       |  |

| Output fall times                   | AUXIN to AUXOUT   | C <sub>L(AUXVOUT</sub> )=0.1uF, I <sub>O(AUXOUT)</sub> =0A                         | 10   |     | 150 | us    |  |

| when card<br>removed (both          | 1.5VIN to 1.5VOUT | $C_{L(1.5VOUT)} = 0.1 uF, I_{O(1.5VOUT)} = 0A$                                     | 10   |     | 150 |       |  |

| CPUSB# and                          | 3.3VIN to 3.3VOUT | $C_{L(3.3VOUT)}$ =20uF, $I_{O(3.3VOUT)}$ =0A                                       | 5    |     | 30  |       |  |

| CPPE# de-                           | AUXIN to AUXOUT   | $C_{L(AUXVOUT)}$ =20uF, $I_{O(AUXOUT)}$ =0A                                        | 5    |     | 30  | ms    |  |

| asserted)                           | 1.5VIN to 1.5VOUT | C <sub>L(1.5VOUT)</sub> =20uF, I <sub>O(1.5VOUT)</sub> =0A                         | 5    |     | 30  |       |  |

|                                     | 3.3VIN to 3.3VOUT | $C_{L(3.3VOUT)}=0.1uF, I_{O(3.3VOUT)}=0A$                                          | 10   |     | 150 |       |  |

|                                     | AUXIN to AUXOUT   | C <sub>L(AUXVOUT</sub> )=0.1uF, I <sub>O(AUXOUT)</sub> =0A                         | 10   |     | 150 | us    |  |

| t <sub>f</sub><br>Output fall times | 1.5VIN to 1.5VOUT | C <sub>L(1.5VOUT)</sub> =0.1uF, I <sub>O(1.5VOUT)</sub> =0A                        | 10   |     | 150 |       |  |

| when SHDN#                          | 3.3VIN to 3.3VOUT | $C_{L(3.3VOUT)}$ =100uF, $R_L$ = $V_{I(3.3VIN)}$ /1A                               | 0.1  |     | 3   |       |  |

| asserted (card is present)          | AUXIN to AUXOUT   | $C_{L(AUXVOUT)}$ =100uF,<br>R <sub>L</sub> =V <sub>I(AUXININ)</sub> /0.250A        | 0.1  |     | 3   | ms    |  |

|                                     | 1.5VIN to 1.5VOUT | $C_{L(1.5VOUT)}$ =100uF,<br>R <sub>L</sub> = $_{VI(1.5VIN)}$ /0.500A               | 0.1  |     | 3   |       |  |

|                                     | 3.3VIN to 3.3VOUT | $C_{L(3.3VOUT)} = 0.1 uF, I_{O(3.3VOUT)} = 0A$                                     | 0.1  |     | 6   |       |  |

|                                     | AUXIN to AUXOUT   | $C_{L(AUXVOUT)}=0.1uF, I_{O(AUXOUT)}=0A$                                           | 0.1  |     | 6   |       |  |

| $T_{pd(on)}$                        | 1.5VIN to 1.5VOUT | $C_{L(1.5VOUT)}$ =0.1uF, $I_{O(1.5VOUT)}$ =0A                                      | 0.1  |     | 6   |       |  |

| Turn on                             | 3.3VIN to 3.3VOUT | $C_{L(3.3VOUT)}$ =100uF, $R_L$ = $V_{I(3.3VIN)}$ /1A                               | 0.1  |     | 6   | ms    |  |

| propagation<br>delay                | AUXIN to AUXOUT   | $C_{L(AUXVOUT)}$ =100uF,<br>R <sub>L</sub> =V <sub>I(AUXININ)</sub> /0.250A        | 0.1  |     | 6   |       |  |

|                                     | 1.5VIN to 1.5VOUT | C <sub>L(1.5VOUT)</sub> =100uF,<br>R <sub>L</sub> = <sub>VI(1.5VIN)</sub> /0.500A  | 0.1  |     | 6   |       |  |

### 9. FUNCTIONAL TRUTH TABLES

### **Truth Table for Voltage Outputs**

| VOLT  | VOLTAGES INPUTS (1) |             |       | LOGIC INPUTS |                    |        | VOLTAGE OUTPUTS(2) |         |                        |

|-------|---------------------|-------------|-------|--------------|--------------------|--------|--------------------|---------|------------------------|

| AUXIN | 3.3VIN              | 1.5VIN      | SHDN# | STBY#        | CP# <sup>(4)</sup> | AUXOUT | 3.3VOUT            | 1.5VOUT | MODE <sup>(3)</sup>    |

| Off   | Χ                   | Х           | X     | Х            | X                  | Off    | Off                | Off     | Off                    |

| On    | Off                 | Off         | 1     | 1            | X                  | Off    | Off                | Off     | Off                    |

| On    | On                  | On          | 1     | 0            | 0                  | Off    | Off                | Off     | Off <sup>(5)</sup>     |

| On    | On                  | On          | 1     | 0            | Х                  | Off    | Off                | Off     | Off <sup>(6)</sup>     |

| On    | Х                   | Х           | 0     | Х            | Х                  | GND    | GND                | GND     | Shutdown               |

| On    | Х                   | Х           | 1     | Х            | 1                  | GND    | GND                | GND     | No Card                |

| On    | On                  | On          | 1     | 0            | 0                  | On     | Off                | Off     | Standby                |

| On    | On →<br>Off         | On →<br>Off | 1     | 1            | 0                  | On     | Off                | Off     | Standby <sup>(7)</sup> |

| On    | On                  | On          | 1     | 1            | 0                  | On     | On                 | On      | Card<br>Inserted       |

- (1) For input voltages, *On* means the respective input voltage is higher than its turn on threshold voltage; otherwise, the voltage is *Off* (for AUX input, *Off* means the voltage is close to zero volt).

- (2) For output voltages, *On* means the respective power switch is turned on so the input voltage is connected to the output; *Off* means the power switch and its output discharge FET are both off; *Gnd* means the power switch is off but the output discharge FET is on so the voltage on the output is pulled down to 0 V.

- (3) Mode assigns each set of input conditions and respective output voltage results to a different name. These modes are referred to as input conditions in the following Truth Table for Logic Outputs.

- (4) CP# = CPUSB# and CPPE# equal to 1 when both CPUSB# and CPPE# signals are logic high, or equal to 0 when either CPUSB# or CPPE# is low.

- (5) STBY# is asserted (logic low) prior to the card being present.

- (6) STBY# is asserted (logic low) prior to the voltage inputs being present.

- (7) The card is inserted prior to the removal of the Primary or Secondary power (either 3.3VIN or 1.5VIN or both) at the input of the ExpressCard power switch, then only the primary and secondary power (both 3.3VOUT and 1.5VOUT) are removed and the auxiliary power is sent to the ExpressCard slot.

### **Truth Table for Logic Outputs**

| II            | NPUT CONDITIONS | LOGIC OUTPUTS |        |            |  |

|---------------|-----------------|---------------|--------|------------|--|

| MODE          | SYSRST#         | RCLKEN (1)    | PERST# | RCLKEN (2) |  |

| Off           |                 | x             | 0      | 0          |  |

| Shutdown      | X               |               |        |            |  |

| No Card       | ^               |               |        |            |  |

| Standby       |                 |               |        |            |  |

| Card Inserted | 0               | Hi - Z        | 0      | 1          |  |

|               | 0               | 0             | 0      | 0          |  |

|               | 1               | Hi - Z        | 1      | 1          |  |

|               | 1               | 0             | 0      | 0          |  |

<sup>(1)</sup> RCLKEN as a logic input in this column. RCLKEN is an I/O pin and it can be driven low externally, left open, or connected to high-impedance terminals, such as the gate of a MOSFET. It must not be driven high externally.

<sup>(2)</sup> RCLKEN as a logic output in this column.

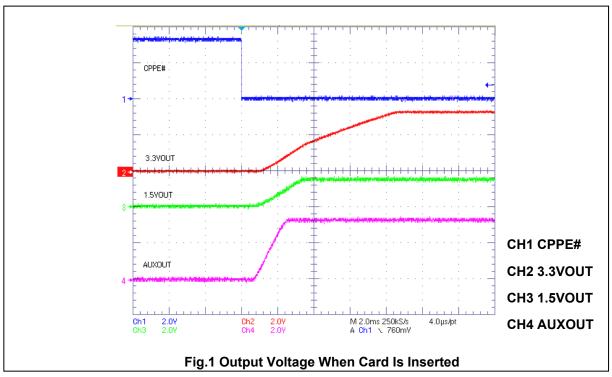

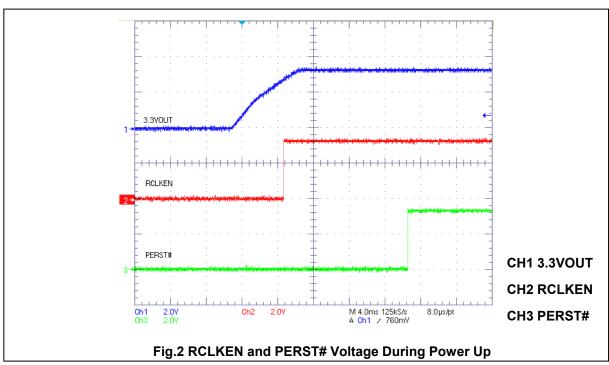

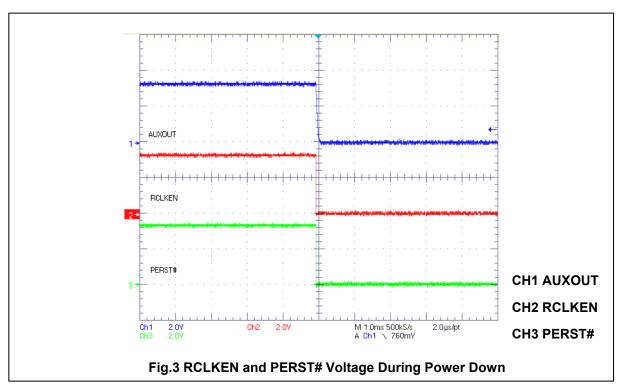

### 10. TYPICAL OPERATING WAVEFORMS

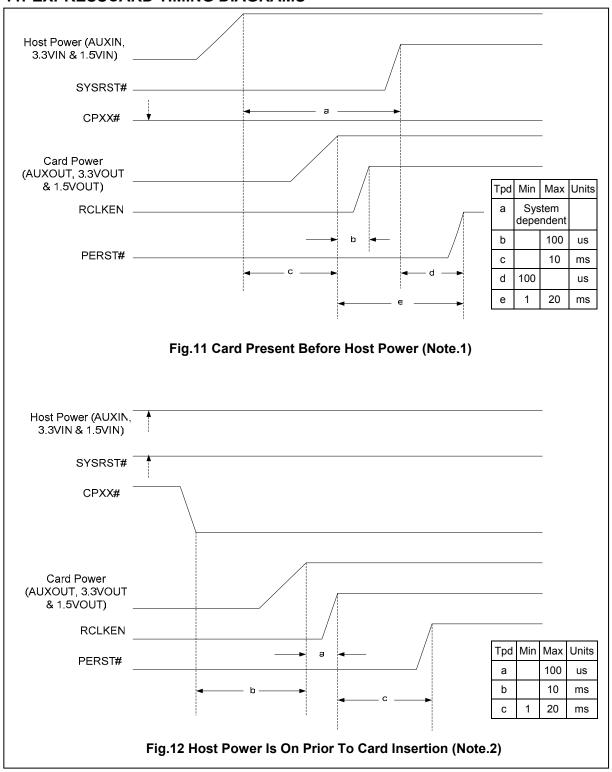

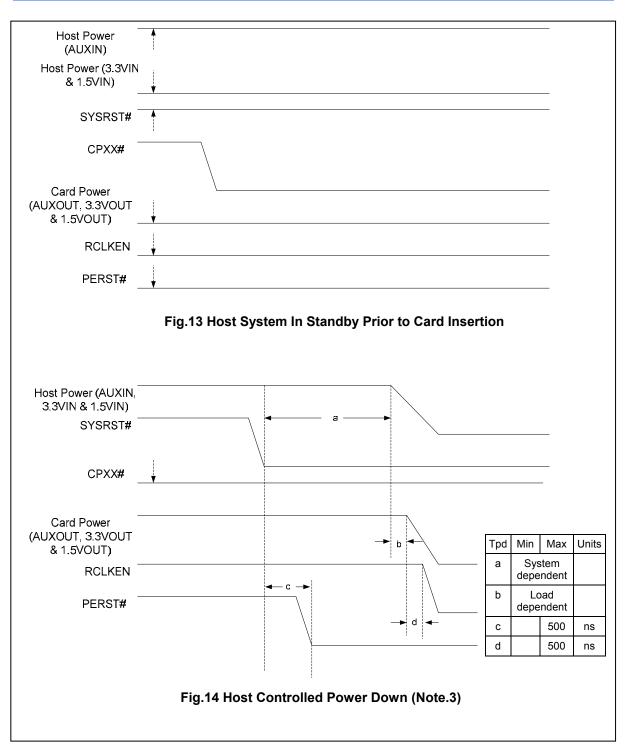

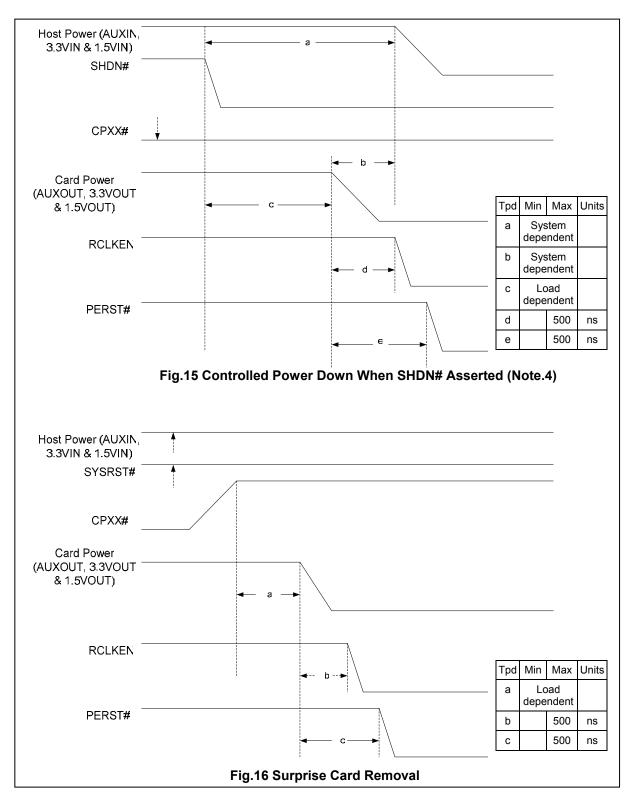

### 11. EXPRESSCARD TIMING DIAGRAMS

- Note.1: According to the electrical specifications of ExpressCard Standard, the minimum propagation delay time of e (Power stable to PERST# inactive) is 1ms.

- Note.2: RCLKEN could be treated as a power good signal when card power is over 86% of nominal voltage.

- Note.3: The propagation delay time of c is SYSRST# assertion to PERST# assertion. The propagation delay time of d is card power is under 86% of nominal voltage to RCLKEN de-assertion.

- Note 4: RCLEKN de-assertion is prior to PERST# assertion when card power lost in any situation.

Publication Date: July 5, 2007 Revision 1.10

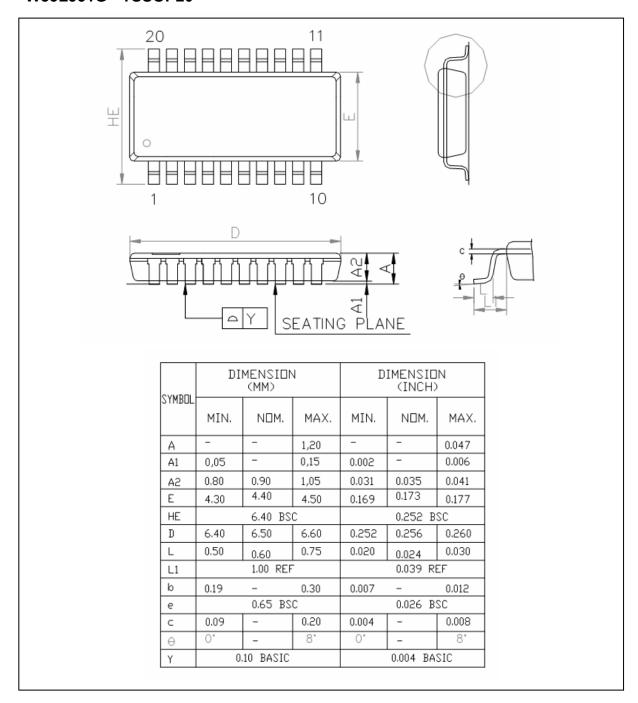

# 12. PACKAGE DIMENSION W83L351G - TSSOP20

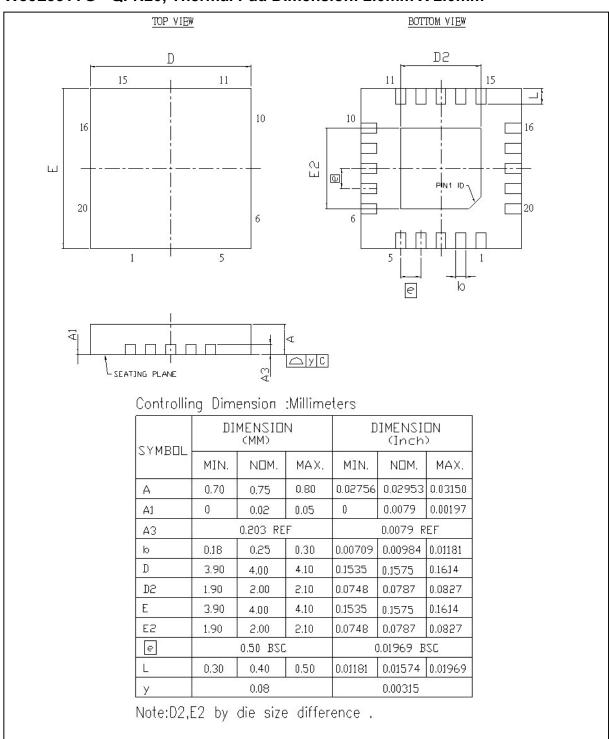

### W83L351YG - QFN20, Thermal Pad Dimension: 2.0mm X 2.0mm

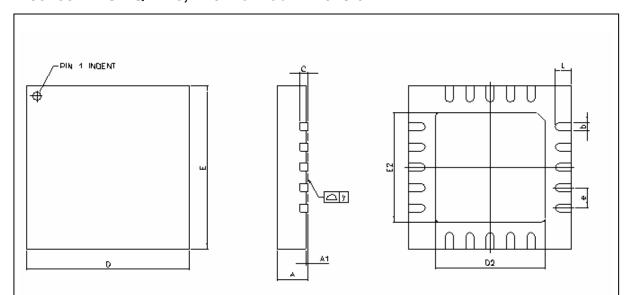

# W83L351YCG - QFN20, Thermal Pad Dimension: 2.7mm X 2.7mm

# Controlling Dimension :Millimeters

| SYMBOLS | DIMENSIONS IN MILLIMETERS |      |       | DIMENSIONS IN INCH |         |         |

|---------|---------------------------|------|-------|--------------------|---------|---------|

|         | MIN                       | NOM  | MAX   | MIN                | NOM     | MAX     |

| А       | 0.70                      | 0.75 | 0.80  | 0.02755            | 0.02952 | 0.03149 |

| A1      | 0.00                      | 0.02 | 0.05  | 0.00000            | 0.00078 | 0.00196 |

| ь       | 0.15                      | 0.23 | 0.30  | 0.00590            | 0.00905 | 0.01181 |

| С       | 0.20 REF.                 |      |       | 0.00787 REF.       |         |         |

| D       | 3.90                      | 4.00 | 4,10  | 0.15354            | 0.15748 | 0,16141 |

| D2      | 2 65                      | 2.70 | 2.75  | 0.10433            | 0.10629 | 0.10826 |

| E       | 3.95                      | 4.00 | 4.05  | 0.15551            | 0.15748 | 0.15944 |

| E2      | 2.65                      | 2.70 | 2.75  | 0.10433            | 0.10629 | 0.10826 |

| e       |                           | 0,50 |       |                    | 0.01968 |         |

| L       | 0.35                      | 0.40 | 0.45  | 0.01377            | 0.01574 | 0,01771 |

| у       | 0.00                      |      | 0.075 | 0.00000            |         | 0.00295 |

Note:D2,E2 by die size difference .

20 Pin TSSOP Package

20 Pin QFN Package

# 13. ORDERING INFORMATION

| PART<br>NUMBER | PACKAGE TYPE                                              | SUPPLIED AS                                               | PRODUCTION FLOW           |

|----------------|-----------------------------------------------------------|-----------------------------------------------------------|---------------------------|

| W83L351G       | 20PIN TSSOP (Pb-free package)                             | E Shape: 74 units/Tube<br>T Shape: 2,500<br>units/T&R     | Commercial, 0°C to +70 °C |

| W83L351YG      | 20PIN QFN (Pb-free package) Thermal Pad Size: 2.0X2.0 mm² | E Shape: 490<br>units/Tray<br>T Shape: 4,000<br>units/T&R | Commercial, 0°C to +70 °C |

| W83L351YCG     | 20PIN QFN (Pb-free package) Thermal Pad Size: 2.7X2.7 nm² | E Shape: 490<br>units/Tray<br>T Shape: 4,000<br>units/T&R | Commercial, 0°C to +70 °C |

### 14. TOP MARKING SPECIFICATION

W83L351G 212345678 606XARA

Left line: Winbond logo

1<sup>st</sup> line: W83L351G – the part number

2<sup>nd</sup> line: Chip lot no

3<sup>rd</sup> line: Tracking code 606 X ARA

606: Packages assembled in Year 06', week 06

X: Assembly house ID ARA: The IC version

Winbond 351YG 636XARB Winbond 351YCG 636XARB

1<sup>st</sup> line: Winbond – company name

2<sup>nd</sup> line: 351YG/351YCG – the part number

3<sup>rd</sup> line: Tracking code <u>636 X ARB</u>

636: Packages assembled in Year 06', week 36

X: Assembly house ID

ARB: The IC version

### **Important Notice**

Winbond products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Winbond products are not intended for applications wherein failure of Winbond products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

Headquarters

No. 4, Creation Rd. III, Science-Based Industrial Park, Hsinchu, Taiwan TEL: 886-3-5770066

FAX: 886-3-5665577 http://www.winbond.com.tw/

Taipei Office 9F, No.480, Rueiguang Rd.,

Neihu District, Taipei, 114, Taiwan, R.O.C. TEL: 886-2-8177-7168 FAX: 886-2-8751-3579

**Winbond Electronics Corporation America**

2727 North First Street, San Jose,

CA 95134, U.S.A. TEL: 1-408-9436666 FAX: 1-408-5441798

**Winbond Electronics Corporation Japan**

7F Daini-ueno BLDG, 3-7-18 Shinyokohama Kohoku-ku, Yokohama, 222-0033 TEL: 81-45-4781881 FAX: 81-45-4781800

Winbond Electronics (Shanghai) Ltd. 27F, 2299 Yan An W. Rd. Shanghai,

200336 China TEL: 86-21-62365999

FAX: 86-21-62365998

Winbond Electronics (H.K.) Ltd. Unit 9-15, 22F, Millennium City, No. 378 Kwun Tong Rd., Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.